In modernen Halbleiter-Testsystemen (ATE, Probe Cards, Load Boards, Interface Boards) entscheidet nicht nur das IC-Design über die Messgüte, sondern zunehmend die Leiterplatte: 34-Lagen-HDI-PCBs mit 0,3 mm Mikrovia-Strukturen und einem 17:1 Seitenverhältnis (Aspect Ratio) sind heute ein kritischer Hebel, um Impedanzschwankungen, Übersprechen und Reflexionen im hochfrequenten/high-speed Umfeld zu reduzieren. Gleichzeitig steigt die Prozesskomplexität – insbesondere bei Bohrpräzision, Backdrill-Kontrolle und der Gleichmäßigkeit der Kupfermetallisierung.

Bei HDI-Leiterplatten beschreibt die Mikrovia eine kleinformatige Via-Struktur (häufig lasergebohrt), die hochdichte Lagenwechsel ermöglicht und Leitungslängen verkürzt. Das Seitenverhältnis (Bohrtiefe zu Bohrdurchmesser) beeinflusst direkt die metallurgische Sicherheit: Je höher das Verhältnis, desto anspruchsvoller werden Wandstärkenverteilung, Porenfreiheit und die verlässliche Durchkontaktierung.

In Testanwendungen, in denen serielle Links im Bereich von 10–28 Gbps (und darüber) auftreten oder wo schnelle Flanken (< 100 ps Anstiegszeit, systemabhängig) dominieren, wird die Via-Geometrie nicht mehr als “Nebenparameter” behandelt. Sie wird zur Signalintegritätsvariable, die in S-Parametern, Eye-Diagrammen und Jitter-Budgets sichtbar wird.

Die Kombination aus kleinem Via-Durchmesser und hohem Seitenverhältnis zwingt die Prozesskette zu engeren Fenstern. Schon kleine Abweichungen bei Bohrung, Desmear, Aktivierung oder Galvanik schlagen sich in Widerstandsdrift, lokalen Hotspots oder im schlimmsten Fall in Intermittents (sporadische Aussetzer) nieder – ein besonders kritischer Fehlerfall im Test, weil er die Reproduzierbarkeit von Messreihen zerstört.

Laserbohrprozesse müssen neben der Trefferlage auch Rundheit, Konizität und Wärmeeinflusszone stabil halten. Bei hochdichten HDI-Aufbauten beeinflusst die Via-Konizität die effektive Via-Induktivität und die Übergangsdiskontinuität. In der Praxis wird die Prozessfähigkeit häufig über Cp/Cpk-Fenster gesteuert; für kritische HDI-Features gelten in vielen Fertigungsumgebungen Cpk-Ziele ≥ 1,33 als Qualitätsmaßstab (merkmal- und werksspezifisch).

Bei 17:1-Strukturen ist die Herausforderung die gleichmäßige Wandstärke über die gesamte Via-Tiefe. Ungleichmäßige Abscheidung führt zu Stromdichte-Spitzen und kann bei Temperaturwechseln zu Mikrorissen beitragen. Industriell werden Microsections/Schliffbilder sowie Inline-Überwachung genutzt; als grobe Orientierung gilt, dass eine Via-Wandstärke im Bereich von ~20–25 µm (applikationsabhängig) in High-Reliability-Szenarien häufig angestrebt wird, während die Gleichmäßigkeit (Throwing Power) den Ausschlag gibt.

Backdrilling entfernt ungenutzte Via-Stubs, die als resonante Elemente wirken können. In High-Speed-Testboards wird die Reststub-Länge häufig als Design-to-Manufacturing-KPI behandelt, weil sie die via-bedingte Reflexion und das Einfügen von Notches im Frequenzgang beeinflusst. Entscheidend ist dabei nicht nur das Bohren selbst, sondern die Koaxialität zur Via und die reproduzierbare Tiefensteuerung.

| SI-/Reliability-Kriterium | Konventionelle Lösung (typisch) | HDI mit optimierter Via/Backdrill (typisch) | Praktischer Nutzen im Test |

|---|---|---|---|

| Impedanz-Variation entlang kritischer Netze | ±10–12% | ±6–8% | Stabilere Kalibrierung, geringere Rework-Quote |

| Übersprechen (NEXT) bei dichter Führung | Baseline | ~10–25% Reduktion möglich | Bessere Bit-Fehlerrate/Noise-Margen |

| Via-Stub-induzierte Resonanzen | häufig sichtbar | deutlich abgeschwächt | Sauberer Frequenzgang, robustere Eyes |

| Intermittents durch Via-/Plating-Risiken | höheres Risiko bei hoher Layerzahl | reduzierbar durch Prozessfenster & Schliffkontrolle | Höhere Testkonsistenz über Zyklen |

Hinweis: Werte sind typische Praxisbereiche aus High-Speed-PCB-Projekten und hängen von Stackup, Material (Df/Dk), Leitergeometrie, Referenzebenen und Validierungsmethodik ab.

Bei hochzuverlässigen Testboards wird die technologische Diskussion selten ohne Normbezug geführt. In der Praxis orientieren sich viele Programme an IPC-6012 (Performance Specification for Rigid Printed Boards), IPC-A-600 (Acceptability of Printed Boards) und für Microvia-spezifische Design-/Fertigungsanforderungen an IPC-2226. Für das Oberflächenfinish und die Lötstellenzuverlässigkeit spielen zudem IPC-nahe Akzeptanzkriterien und kundenspezifische Spezifikationen eine Rolle.

Typische Nachweise, die in Halbleiter-Testprojekten regelmäßig eingefordert werden:

Der Mehrwert von HDI entsteht nicht allein durch “kleiner und dichter”, sondern durch nachweisbar beherrschte Prozessparameter – mit Dokumentation, die in Audits und Ramp-ups standhält.

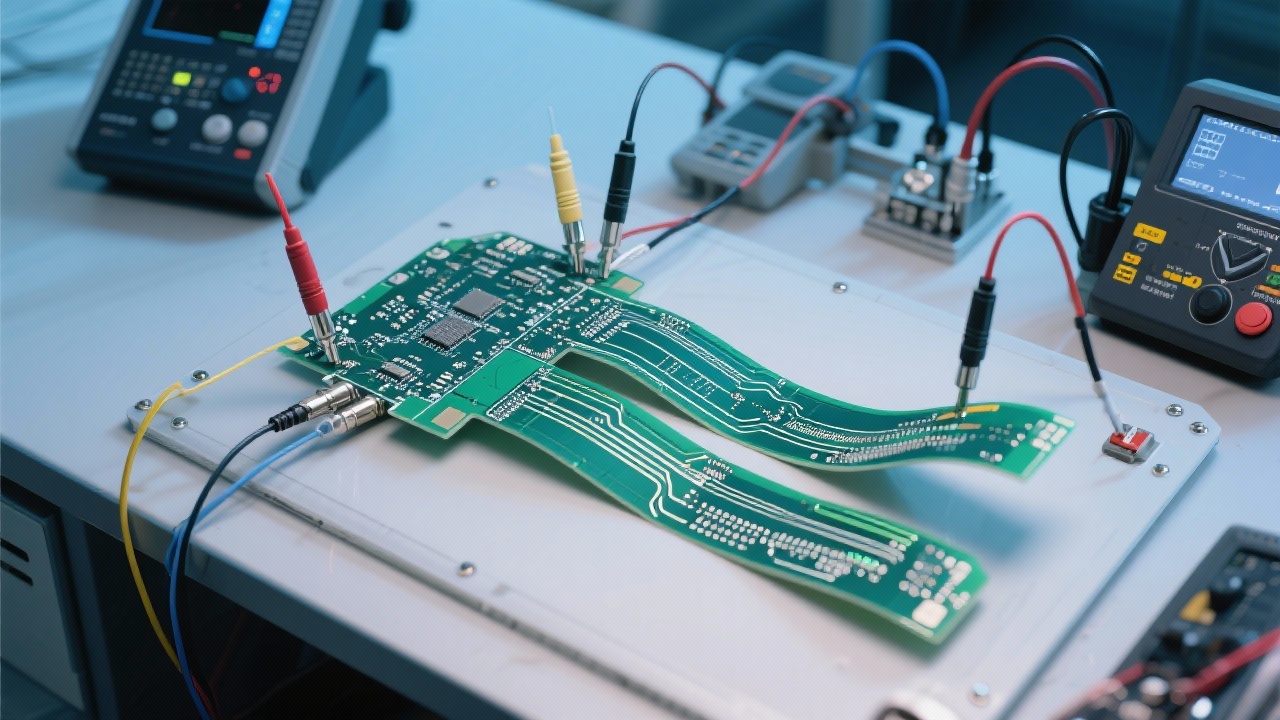

In einem typischen Load-Board-Szenario mit hoher Lagenzahl und dichtem Routing wurden High-Speed-Differentialpaare über mehrere Lagenwechsel geführt. In der Ausgangskonfiguration traten bei bestimmten Frequenzbereichen reproduzierbare Einbrüche im Transferverhalten auf, die sich in der Systemvalidierung als schwankende Margin zeigten. Nach Umstellung auf eine HDI-Architektur mit 0,3 mm Mikrovia-Features, konsequentem Backdrill und eng kontrollierter Kupfermetallisierung wurde die Streuung in den TDR-Profilen sichtbar reduziert; parallel sank die Anfälligkeit für sporadische Ausreißer bei wiederholten Steck-/Testzyklen.

Entscheidend war weniger “ein einzelner Trick” als das Zusammenspiel: präzise Laserprozesse, saubere Stub-Reduktion und gleichmäßige Kupferverteilung – also genau jene Faktoren, die bei 17:1-Aspektverhältnissen über Erfolg oder Fehlersuche entscheiden.

Konventionelle Durchkontaktierungen und weniger fein abgestimmte Stackups sind in vielen Industriebereichen weiterhin sinnvoll. Im Halbleiter-Testumfeld treten jedoch typische Limitierungen deutlicher auf:

Das erklärt, warum HDI in fortgeschrittenen Testplattformen nicht als Luxus gilt, sondern als Engineering-Voraussetzung, um reproduzierbare Messfenster zu sichern.

Der Trend geht zu weiter steigender Portdichte, höheren Datenraten und strengeren Jitter-Budgets. Entsprechend rücken noch feinere Via- und Pad-Optimierung, prozessstabile Backdrill-Strategien und verbesserte Materialsysteme (niedriger Df, stabiler Dk über Temperatur) in den Fokus. In vielen Roadmaps wird außerdem die systematische Nutzung von S-Parameter-Validierung und Design-for-Manufacturing-Regeln als verbindlicher Teil der Angebots-/Freigabekette etabliert.

Für Teams in Packaging, PCB-Prozessoptimierung und Testintegration bedeutet das: Die Auswahl von 0,3 mm Mikrovia-Parametern und die Beherrschung hoher Aspect Ratios sind weniger “Spezialthemen” als ein praktischer Standard, um die nächste Generation von Testplattformen robust zu skalieren.

Wenn ein Halbleiter-Testboard nicht nur “funktionieren”, sondern über viele Zyklen messstabil bleiben soll, ist die Abstimmung von Stackup, Via-Struktur, Backdrill-Fenstern und Kupfermetallisierung entscheidend. Unser Team unterstützt bei DFM-Review, Coupon-Strategie, Impedanzzielsetzung und Fertigungsfreigabe – mit dokumentierbaren Qualitätsnachweisen (Microsections, Backdrill-Reports, TDR-Protokolle).

Senden Sie Stackup, Zielimpedanzen, Layer-Transition-Plan und Backdrill-Anforderungen. Rückmeldung typischerweise innerhalb von 1–2 Werktagen.

Technischer Kontakt: [email protected] | Tel.: +49 0000 000000

-1.png?x-oss-process=image/resize,h_800,m_lfit/format,webp)