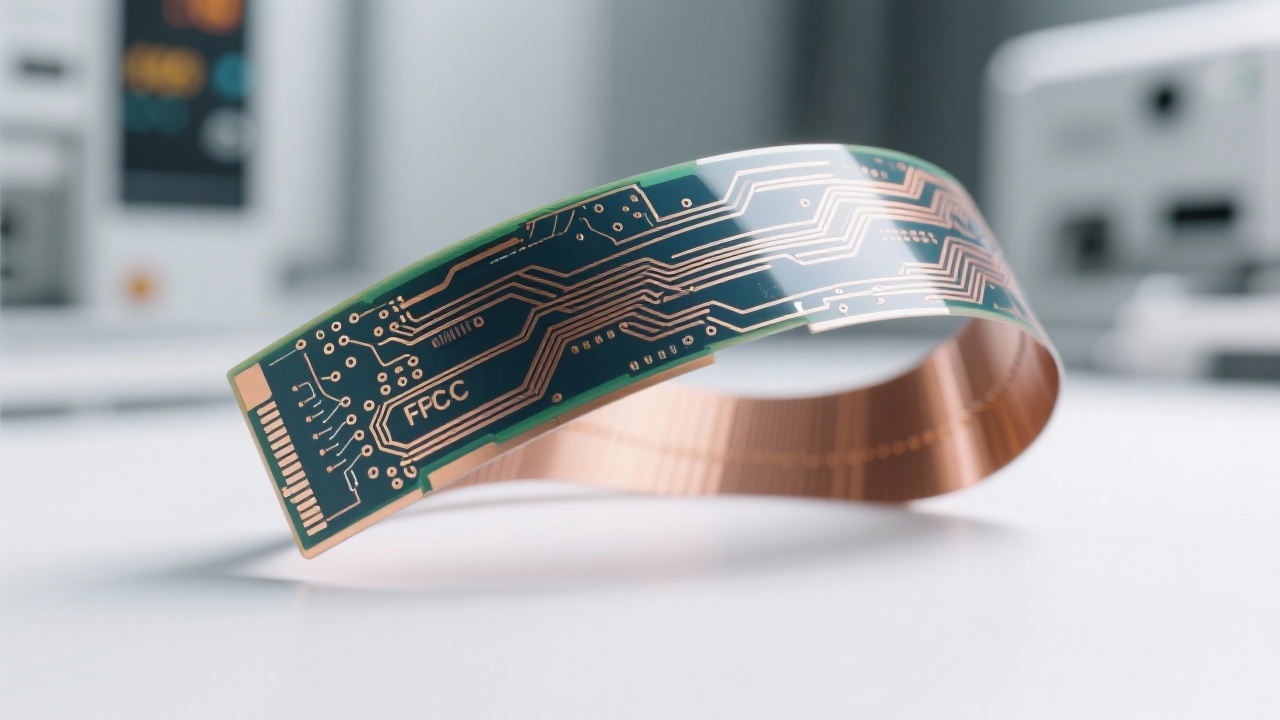

In hochverdichteten Anwendungen wie der Konsumelektronik oder Medizintechnik gilt die Optimierung der elektromagnetischen Verträglichkeit (EMV) und die Minimierung von Signalübersprechen als entscheidender Erfolgsfaktor bei der Entwicklung flexibler Leiterplatten (FPCs). Dieser Beitrag beleuchtet zentrale Designstrategien zur EMV-Verbesserung und zeigt anhand realer Praxisbeispiele, wie eine methodische Planung von Layout und Leiterbahnen signifikant Störeinflüsse reduziert.

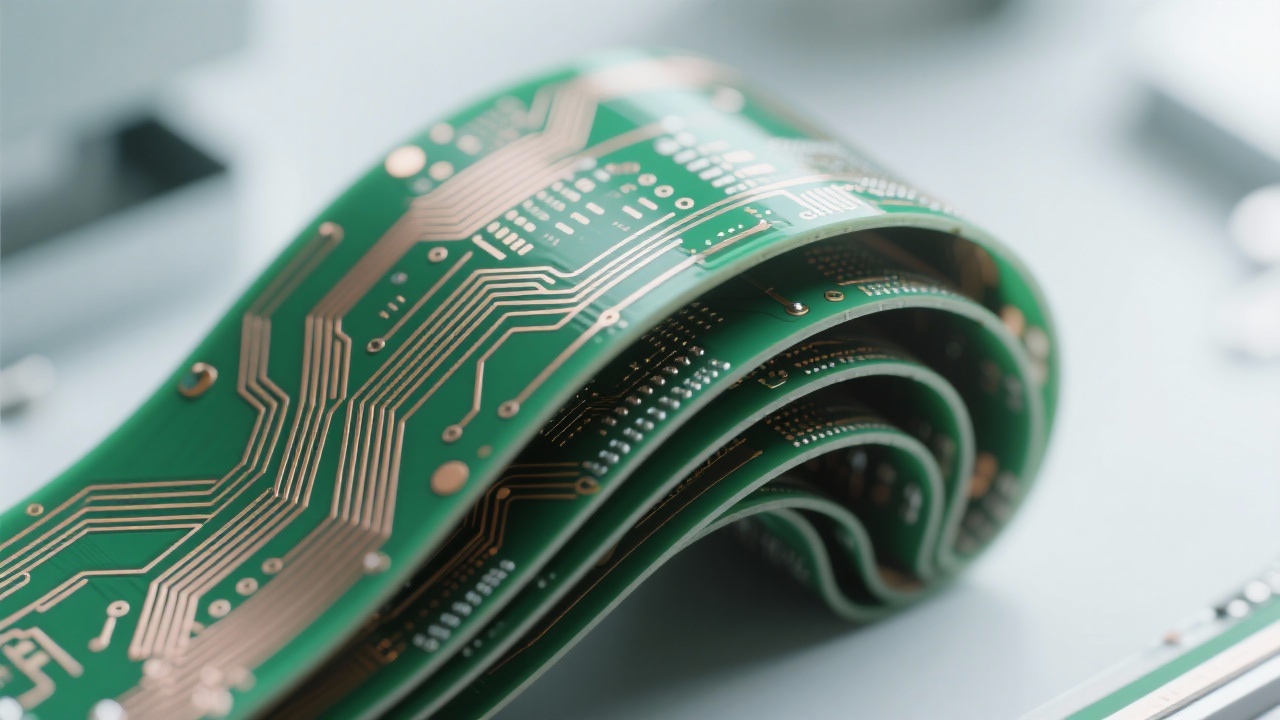

Eng gesteckte Leiterbahnen im Bereich von 0,1 mm Breite und Abstand steigern die Gefahr elektromagnetischer Störungen durch kapazitive und induktive Kopplung. Dies erzeugt je nach Frequenzspektrum und Umgebung unerwünschtes Signalübersprechen, das die Funktionalität sensibler Elektronik beeinträchtigen kann. Neben der EMV stellt die mechanische Belastbarkeit in flexiblen Baugruppen eine weitere zentrale Herausforderung dar, da geringfügige Fertigungstoleranzen die Zuverlässigkeit nachhaltig beeinflussen.

Eine physikalisch begründete Trennung kritischer Signale voneinander ist essenziell. Die Aufteilung in separate Gutzonen für Hochfrequenz-, Analog- und digitale Leitungen sowie das Vermeiden paralleler, langgezogener Leiterbahnen helfen, Übersprechen deutlich zu minimieren. Ebenfalls entscheidend sind ausreichende Rückstromflächen und leitfähige Schirmungen, die leitfähige Kopplungen reduzieren.

Aktuelle Präzisionsfertigungen erlauben minimalbreite von 0,1 mm für Leiterbahnen und Zwischenräume. Die gezielte Anpassung dieser Maße an Signalfrequenzen und Impedanzparameter steuert die elektromagnetische Streuung. Designregeln empfehlen mindestens 0,1 mm als sicheren Abstand bei Signalfrequenzen bis zu 1 GHz.

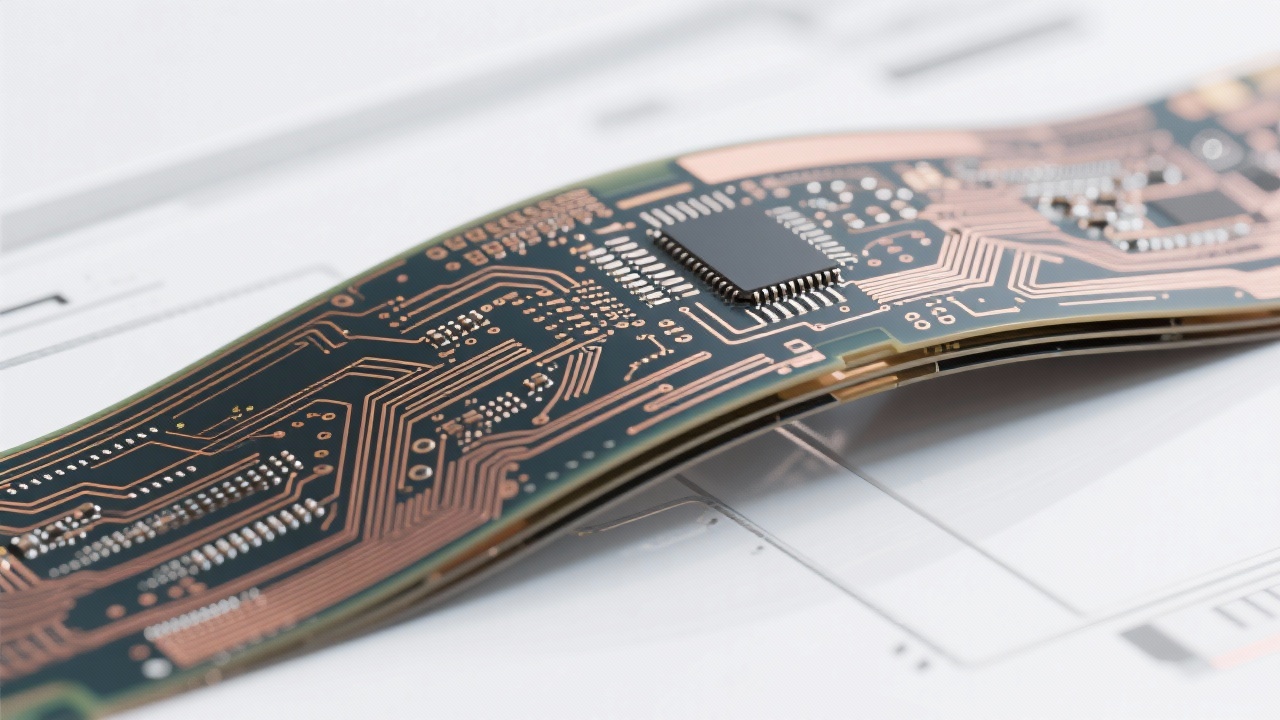

Minimale Bohrungen mit Durchmessern ab 0,2 mm ermöglichen komplexe mehrschichtige Strukturen, ohne unerwünschte Induktionseffekte hervorzurufen. Die Auswahl von Via-Anordnungen in Kombination mit optimierten Schirmlagen ist ausschlaggebend für reduzierte parasitäre Kapazitäten.

Ein zu dicht nebeneinander geführtes Sensormodul eines tragbaren medizinischen Prüfsystems zeigte periodische Störungen im hochfrequenten Bereich von 800 MHz. Durch den gezielten Einsatz von differenziell geführten Leitungen, Vergrößerung des Abstandes von 0,05 mm auf 0,1 mm und Implementierung einer zusätzlichen Kupferschirmung konnte das Übersprechen um ca. 75 % reduziert werden. Die Fertigung erfolgte unter Verwendung von 0,2 mm Mikrovias, die präzise kontaktierte Verbindungen auch bei engsten Bauteilabständen absicherten. Ergebnis war eine signifikante Erhöhung der Messgenauigkeit und Systemstabilität.

Mittels hochpräziser Bohr- und Graviertechnik können Leiterbahnen und Vias heute mit Toleranzen von ±10 µm zuverlässig hergestellt werden, wodurch engste Designvorgaben erfüllt werden. Die Serienfertigung von FPCs mit bis zu 8 Lagen und einer minimalen Leiterbahnbreite von 0,1 mm ist industrieller Standard, der Raum für Innovationen auch in engsten Baugruppen schafft.

„Die EMV-Anforderungen gemäß IEC 61000-4 sowie die Einhaltung von UL 94 V-0 als Flammwidrigkeitsstandard sichern neben RoHS-konformer Materialauswahl die Sicherheit und Zuverlässigkeit von FPC-Lösungen im industriellen und medizinischen Einsatz.“

Zertifizierungen nach ISO 9001 sichern zudem reproduzierbare Qualität und stellen sicher, dass Prozesskontrollen den hohen Anforderungen an EMV und Fertigungsgenauigkeit gerecht werden.

Unsere FPC-Lösungen wurden erfolgreich in anspruchsvollen medizinischen Geräten eingesetzt und bieten ein Optimum aus miniaturisiertem Design, EMV-Optimierung und Produktionssicherheit. Entdecken Sie, wie wir Ihre Projekte mit präzisen Mehrlagen-FPCs auf das nächste Level heben.

-1.png?x-oss-process=image/resize,h_800,m_lfit/format,webp)