Die schnelle und zuverlässige Fertigung von Doppel-Lagen-Leiterplatten (Printed Circuit Boards, PCB) spielt eine zentrale Rolle in der Elektronikentwicklung und -produktion. Von der präzisen Designeingabe bis hin zur abschließenden elektrischen Prüfung erfordert der Prozess eine hohe technische Expertise und konsequente Qualitätskontrolle. Dieser Leitfaden beleuchtet die wichtigsten Technologie- und Prozessschritte bei der Herstellung von Doppel-Lagen-PCBs, demonstriert praxisrelevante Verfahren wie Ätzung, Laminierung, Bohren und die maßgeblichen Oberflächenbehandlungen LF HAL, ENIG und OSP.

Der Herstellungsprozess beginnt mit einem fehlerfrei erstellten Design-Input unter Berücksichtigung aller relevanten Designregeln und Auftragsspezifikationen. Die Daten werden sorgfältig geprüft, um spätere Fehlerquellen bei der Schichtausrichtung und der Bohrpositionierung zu minimieren. Eine strikte Einhaltung der Gerber- und Excellon-Standards gewährleistet, dass die CAD-Daten reibungslos mit chemischen und mechanischen Bearbeitungsverfahren harmonieren.

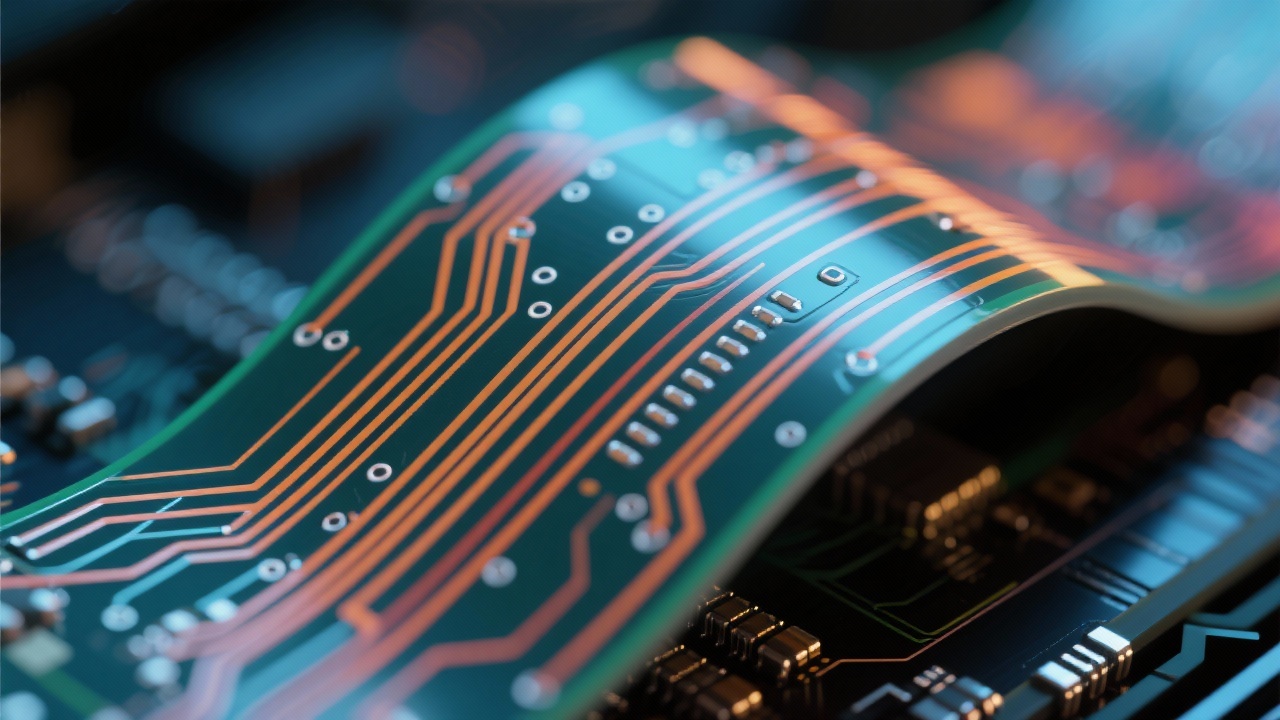

Die Ätztechnik ist ein kritischer Schritt, bei dem Kupfer auf den äußeren Schichten präzise entfernt wird. Durch moderne photolithografische Verfahren wird ein Auflösungsvermögen von bis zu 25μm realisiert, um feine Leiterbahnen zu erzeugen. Anschließend folgt die Laminierung, bei der zwei Basismaterialien durch Hitze und Druck verbunden werden. Hierbei ist eine optimale Temperaturführung (typischerweise 180–200 °C) und Druckverteilung essenziell, um Delamination und Lufteinschlüsse zu vermeiden.

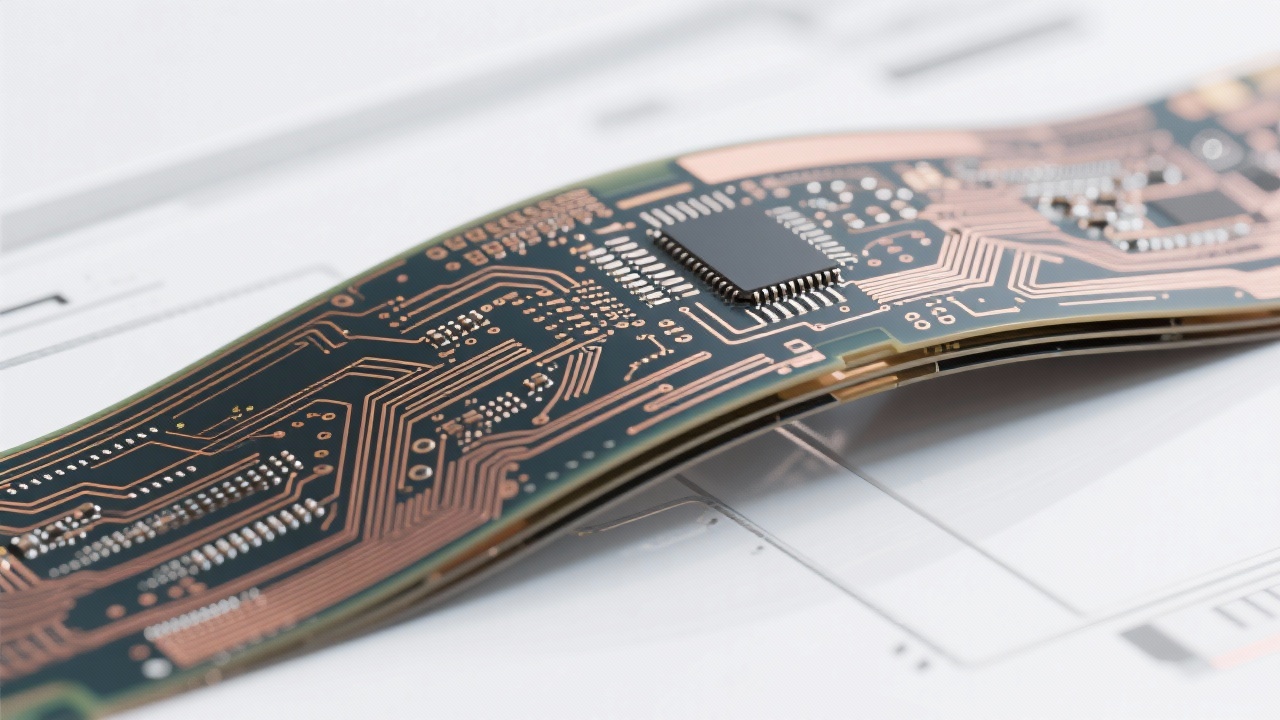

Das Bohren der Durchkontaktierungen (Vias) erfolgt mit CNC-gesteuerten Systemen, die eine Positioniergenauigkeit von ±5μm garantieren. Dabei kommen häufig Hartmetall- oder Diamantbohrer zum Einsatz. Die Bohrqualität entscheidet maßgeblich über die elektrische Zuverlässigkeit und die Lötbarkeit der PCB. Die nachfolgende Plattierung sichert den leitfähigen Kontakt zwischen den Lagen.

Die Auswahl der Oberflächenveredelung beeinflusst die Lötbarkeit, Korrosionsbeständigkeit und Lebensdauer der Leiterplatten. Drei häufig genutzte Verfahren sind:

Die Entscheidung für eine geeignete Oberflächenbehandlung richtet sich nach Anwendungsbedarf, Haltbarkeit und Budgetrahmen. Studien zeigen, dass ENIG-Oberflächen die Fehlerrate bei automatisierter Bestückung um bis zu 40 % verglichen mit LF HAL senken können.

Flying-Probe-Tests sind besonders für Kleinserien und Prototypen geeignet, da sie flexibel und schnell Fehlstellen wie Kurzschlüsse, Unterbrechungen und Lötfehler detektieren können. Durch hochpräzise Nadeln, die Kontaktpunkte einzeln abfahren, werden bis zu 100 % der elektrischen Verbindungspunkte geprüft. Die Methode reduziert Testzeiten um 30 % verglichen mit traditionellen Nadelbett-Testsystemen.

Die Eigenfertigung von Schlüsselprozessen ermöglicht stringentere Qualitätskontrollen, individuelle Prozessanpassungen und eine signifikante Reduktion der Durchlaufzeiten. Beispielsweise konnte durch eine optimierte Schichtlaminierung und direkt integrierte Beschaffung die Lieferzeit für Doppel-Lagen-PCBs auf unter 7 Werktage verkürzt werden – ein Wettbewerbsvorteil in globalen Beschaffungsmärkten mit ständig wachsendem Zeitdruck.

Durch den Einsatz intelligenter Fertigungsplanungssoftware sowie die Integration logistischer Echtzeit-Tracking-Systeme konnte ein Hersteller den Ausstoß bei gleichbleibender Qualität um 15 % steigern und die termingerechte Lieferung in Europa, Nordamerika und Asien mit 98 % Zuverlässigkeit realisieren. Solche Lean-Management-Methoden sind essenziell für die Anpassung an volatilen Bedarf und Just-in-Time-Lieferketten.