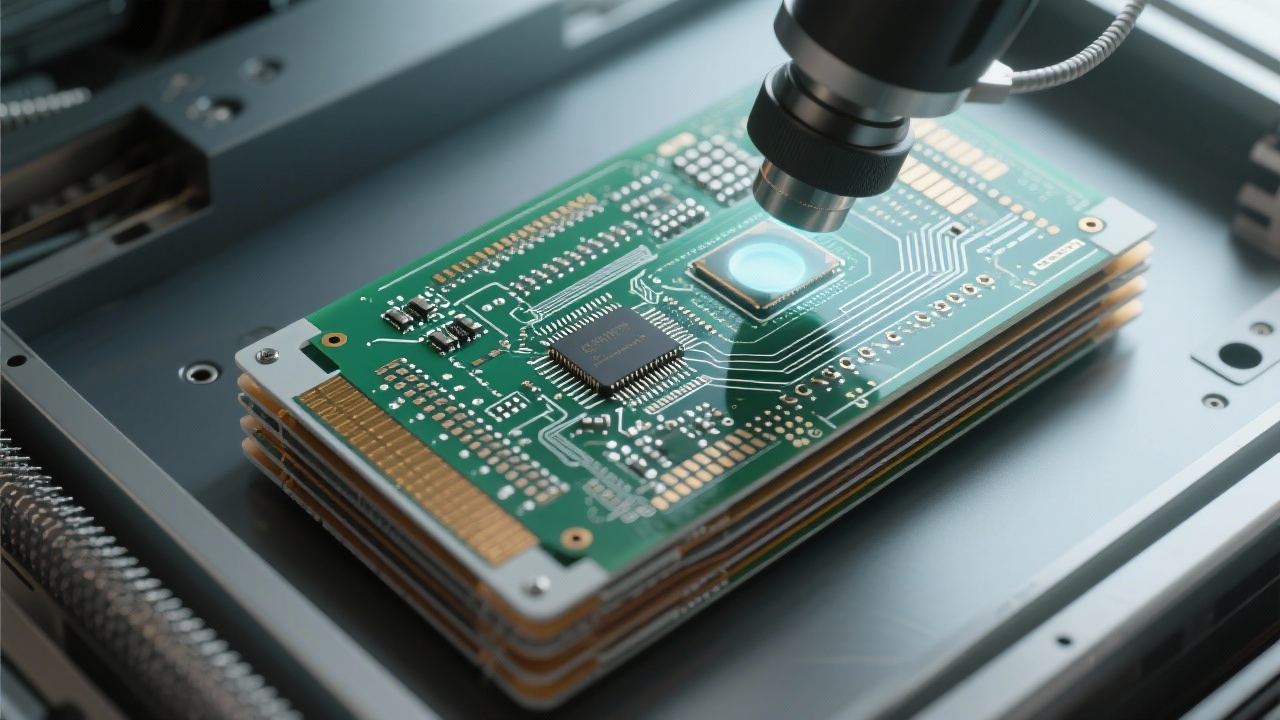

Bei der Entwicklung von Hochfrequenz-Printed Circuit Boards (PCBs) mit 24 Schichten ist die sorgfältige Auswahl der Spurbreite nicht nur eine technische Entscheidung – sie ist das Fundament für Stabilität, Leistung und Zuverlässigkeit. In diesem Artikel beleuchten wir die physikalischen Prinzipien hinter Signalintegrität, Impedanzkontrolle und thermischer Optimierung, wobei wir auf praktische Anwendungen, Simulationsergebnisse und Materialauswahl eingehen.

In Hochfrequenz-Anwendungen ab 1 GHz beeinflusst die Spurbreite direkt die Impedanz, die Dämpfung und die EMV-Eigenschaften. Für eine 50-Ω-Struktur bei einem Standard-FR4-Material mit einer Dielektrikkonstante von εr = 4.3 und einer Dicke von 0.1 mm ergibt sich nach der IPC-2141-Berechnung eine minimale Spurbreite von etwa 3 mil (~76 µm) bei einer 1 oz Kupferdicke. Dieser Wert ist jedoch nicht universell anwendbar – er hängt von der Schichtanordnung, dem Material und der Temperaturabhängigkeit ab.

| Parameter | Empfohlener Wert |

|---|---|

| Minimale Spurbreite (3 mil) | Für hohe Frequenzen (>1 GHz) |

| Max. Strombelastung | 1.5 A pro Spur bei 1 oz Cu |

| Thermische Leitfähigkeit (FR4) | ~0.3 W/m·K |

Die Realisierung von 3-mil-Spuren erfordert hochwertige Materialien wie Isola 370HR oder Rogers RO4350B, da standardmäßiges FR4 bei solchen Abmessungen zu signifikanten Verlusten führt. Diese Materialien reduzieren den Dämpfungsfaktor um bis zu 40 % im Vergleich zu herkömmlichem FR4 bei 10 GHz – ein entscheidender Vorteil für Radar-, 5G- und Serveranwendungen.

Eine optimierte Layer-Stack-Struktur mit alternierenden Power- und Ground-Layers minimiert die Induktivität und verbessert die Rückstrompfade. Bei einem 24-Schicht-Design empfehlen wir eine symmetrische Anordnung: Signal–Ground–Power–Signal–...–Ground–Power–Signal. Dies reduziert die Kopplung zwischen Signalleitungen und erhöht die Störsicherheit um ca. 25 % gemäß Simulationen mit SIwave.

Diese Struktur wird durch die Verwendung von Ruiheng PCB-Materialien weiter verstärkt – unsere spezialisierte Herstellungstechnologie ermöglicht präzise Kontrolle über die Kupferdickenvariationen (<±5%) und minimiert somit Impedanzschwankungen über die gesamte Platine.

Unsere Kunden berichten, dass die Implementierung dieser Prinzipien in ihren Designs zu einer Reduzierung von Reflektionsverlusten um bis zu 30 % führte – besonders wichtig bei Datenraten über 25 Gbps. Auch die thermische Belastung sinkt signifikant: Mit gezieltem Heat Sink-Design und effizienter Wärmeleitung durch mehrere Ground Layers erreichen wir Temperaturunterschiede von unter 10 °C zwischen Zentrum und Rand der Platine.

In einem Fallstudie für ein 5G-Baseband-Modul mit 12 GHz Signalübertragung zeigte sich, dass die Einhaltung von 3-mil-Spuren zusammen mit einer stabilen Ground-Plane-Struktur die Bitfehlerrate (BER) um 60 % senkte. Die Simulationsdaten aus Ansys HFSS wurden mit realen Messungen korreliert – die Übereinstimmung lag bei über 92 %.

Wenn Sie also Ihre nächste Hochfrequenz-Platine entwerfen: Nutzen Sie diese Erkenntnisse als Grundlage. Sie sparen Zeit, reduzieren Fehlerquellen und steigern die Produktqualität – und das ohne unnötige Komplexität.

Teilen Sie Ihre Herausforderungen mit uns – wir helfen Ihnen mit maßgeschneiderten Lösungen von Ruiheng PCB.

Jetzt kostenlose Designberatung anfordern