Im Bereich der Halbleiter-Testtechnik hat die Präzision von Hochdichte-Interconnect-(HDI)-Printed Circuit Boards (PCBs) einen entscheidenden Einfluss auf die Zuverlässigkeit und Genauigkeit der gesamten Testprozesse. Ein maßgeblicher Faktor hierfür ist die Warpage, also die Verformung der Leiterplatte. Während die IPC-II-Norm einen Grenzwert von 0,75 % für die Warpage festlegt, hat die Industrie einen neuen Maßstab von 0,5 % etabliert – ein Schritt, der nicht nur technische Herausforderungen mit sich bringt, sondern auch die Performance von Testanlagen entscheidend verbessert.

Die IPC-6012- Norm, die für die Qualitätsanforderungen an Leiterplatten weltweit gültig ist, definiert in ihrer Klasse II (IPC-II) einen maximal zulässigen Warpage-Wert von 0,75 % für Leiterplatten. Dieser Wert war lange Zeit als ausreichend angesehen, um die meisten Anwendungen zu erfüllen. Mit der zunehmenden Miniaturisierung von Halbleitern und der Steigerung der Pin-Dichten in HDI-PCBs hat sich jedoch die Anforderung an die Ebenheit der Leiterplatten drastisch erhöht.

Ein Warpage-Wert von 0,5 % bedeutet, dass eine Leiterplatte mit einer Größe von 300 mm x 300 mm eine maximale Verformung von nur 1,5 mm aufweist. Dieser strengere Standard ist besonders für Hochleistungsanwendungen wie Halbleiter-Testgeräte unerlässlich, da selbst minimale Verformungen zu Fehlern bei der Chip-Befestigung (SMT) oder der Kontaktierung durch Testproben führen können.

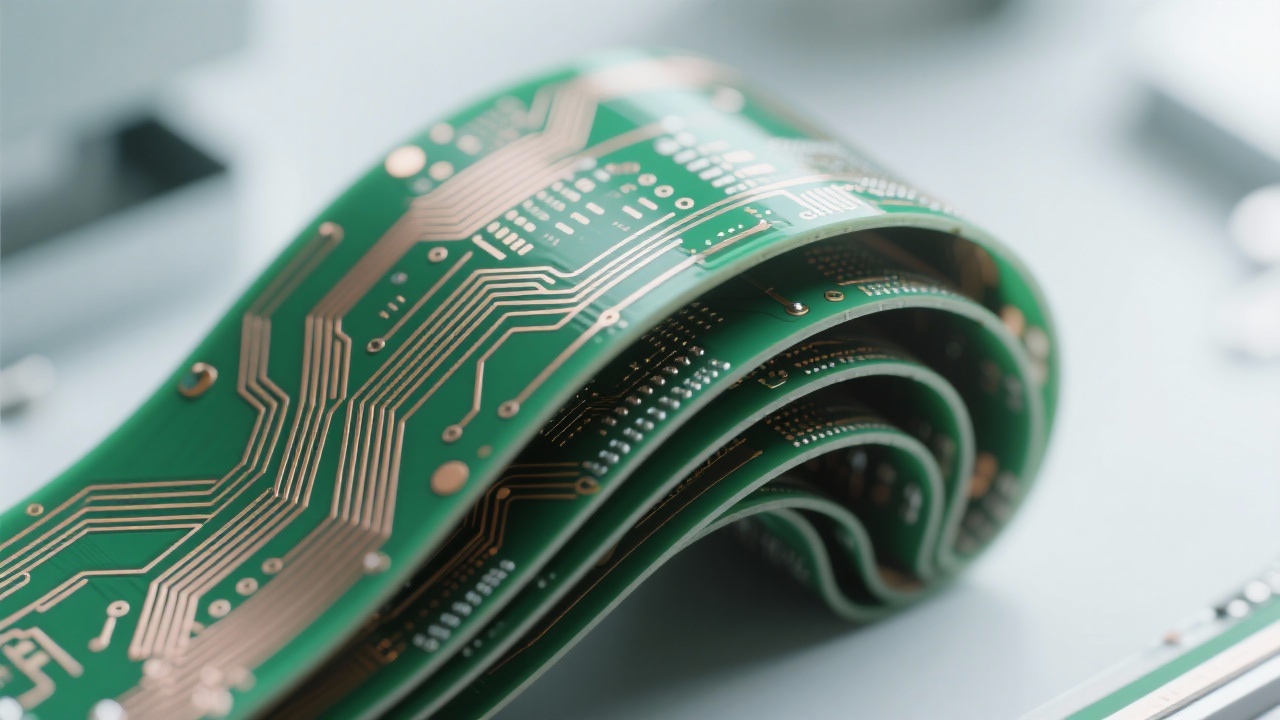

Die Herstellung von HDI-PCBs mit einer Warpage von unter 0,5 % erfordert eine Kombination aus fortschrittlicher Design-Engineering, hochpräziser Fertigungstechnologie und strenger Prozesskontrolle. Besonders bei Mehrschichtdesigns, wie dem Beispiel eines 34-lagigen HDI-PCBs mit einem 1:32:1-Stackup, treten komplexe Spannungsverhältnisse auf, die die Warpage beeinflussen.

Innerhalb eines HDI-PCB-Stackups variieren die Kupferdicken je nach Funktionsanforderung. Dickere Kupferlagen (z. B. 70 µm) für Strombahnen und dünnere Schichten (z. B. 12 µm) für Signalverbindungen können zu ungleichen Wärmeausdehnungskoeffizienten führen. Ohne entsprechende Kompensationsmaßnahmen resultiert dies in unkontrollierter Warpage.

Unsere Ingenieure verwenden spezialisierte Simulationstools, um die Spannungsverteilung in Abhängigkeit von Kupferdickenänderungen vorherzusagen. Durch eine optimierte Anordnung der Schichten und die Verwendung von Hochtemperaturharzen mit geringem Schrumpfverhalten gelingt es uns, die Warpage auf unter 0,5 % zu begrenzen – selbst bei 34-lagigen Designs.

Die deutsche Fertigungstechnologie steht weltweit für Präzision und Zuverlässigkeit. In unserem Produktionszentrum in Bayern verwenden wir fortschrittliche Pressanlagen mit dynamischer Druck- und Temperatursteuerung, die eine gleichmäßige Aushärtung der Leiterplatten gewährleisten. Darüber hinaus setzen wir eine patentierte kombinierte Elektroplattierungstechnik ein, die eine homogene Kupferabscheidung sicherstellt und somit Spannungen reduziert.

Die Einhaltung eines Warpage-Werts von 0,5 %带来 nicht nur technische Prestige, sondern auch messbare wirtschaftliche Vorteile. In unseren Langzeittests mit Kunden aus der Halbleiter-Testbranche konnten wir folgende Ergebnisse nachweisen:

Ein herausragendes Beispiel ist ein Projekt mit einem führenden Hersteller von Halbleiter-Testsystemen. Durch die Integration unserer HDI-PCBs mit 0,5 % Warpage konnte der Kunde die Testgenauigkeit für 7nm-Chips um 15 % steigern und die Produktionsausbeute seiner Testanlagen um 9 % verbessern.

Die Einhaltung von 0,5 % Warpage ist kein Zufallsergebnis, sondern das Ergebnis einer durchdachten Kombination aus Design-Expertise, fortschrittlicher Fertigungstechnologie und strenger Qualitätskontrolle. Nicht jede Herstellerin kann diese hohen Standards gewährleisten – besonders bei komplexen Mehrschichtdesigns über 20 Lagen.

Unsere mehr als 15-jährige Erfahrung in der Produktion von HDI-PCBs für die Halbleiter-Industrie, kombiniert mit unserem Deutschland-basierten Fertigungszentrum, ermöglicht es uns, maßgeschneiderte Lösungen zu liefern, die genau Ihren Anforderungen entsprechen. Von der Prototypenentwicklung bis zur Massenproduktion – wir begleiten Sie in jeder Phase Ihres Projekts.

Kontaktieren Sie uns noch heute, um ein individuelles Beratungsgespräch zu Ihrer HDI-PCB-Anforderung zu vereinbaren und erfahren Sie, wie unsere 0,5 % Warpage-Lösung Ihre Testgenauigkeit und Produktivität steigern kann.

Jetzt unverbindlich beraten lassenDie Welt der Halbleiter-Testtechnik wartet nicht – und weder sollten Sie. Nutzen Sie die Vorteile der neuesten HDI-PCB-Technologie und setzen Sie sich von Ihrer Konkurrenz ab. Mit der richtigen Partnerin an Ihrer Seite sind die Grenzen der Präzision nur eine Frage der Einstellung – oder besser gesagt: der Warpage.