在高速多层PCB设计中,阻抗控制是保障信号完整性和设备稳定运行的核心技术。随着5G基站及高频通信模块需求的爆发,单端50欧姆与差分100欧姆阻抗标准的精准把控,成为提升高速信号传输质量的关键。本文将深入解析阻抗控制基础原理、材料选择及制造公差对阻抗稳定性的保障机制,结合实际通信领域案例,探讨阻抗测量与AOI检测技术,助力研发工程师提升品质管控水平,实现领先的高频高速PCB制造解决方案。

阻抗控制是PCB设计中的命脉,特别是在高速信号传输环境中。常见的单端阻抗规范为50欧姆,差分阻抗规范为100欧姆,它们直接影响信号的反射、串扰及时间延迟。若阻抗匹配不良,信号将产生反射与失真,导致通信质量严重受损。基于传输线理论,使用合适的trace宽度及介质厚度,配合高性能低损耗介电材料,是实现精准阻抗控制的第一步。

以5G基站及高频通信模块为例,阻抗匹配设计需针对复杂多层结构及高频信号特性进行优化。工程师常结合电磁仿真工具,模拟信号路径阻抗分布,调整焊盘布局、层间距及走线参数,确保单端或差分阻抗精度控制在±5%的制造公差范围内。此做法有效降低信号反射率(S11值可降至-20dB以下),优化信号完整性。

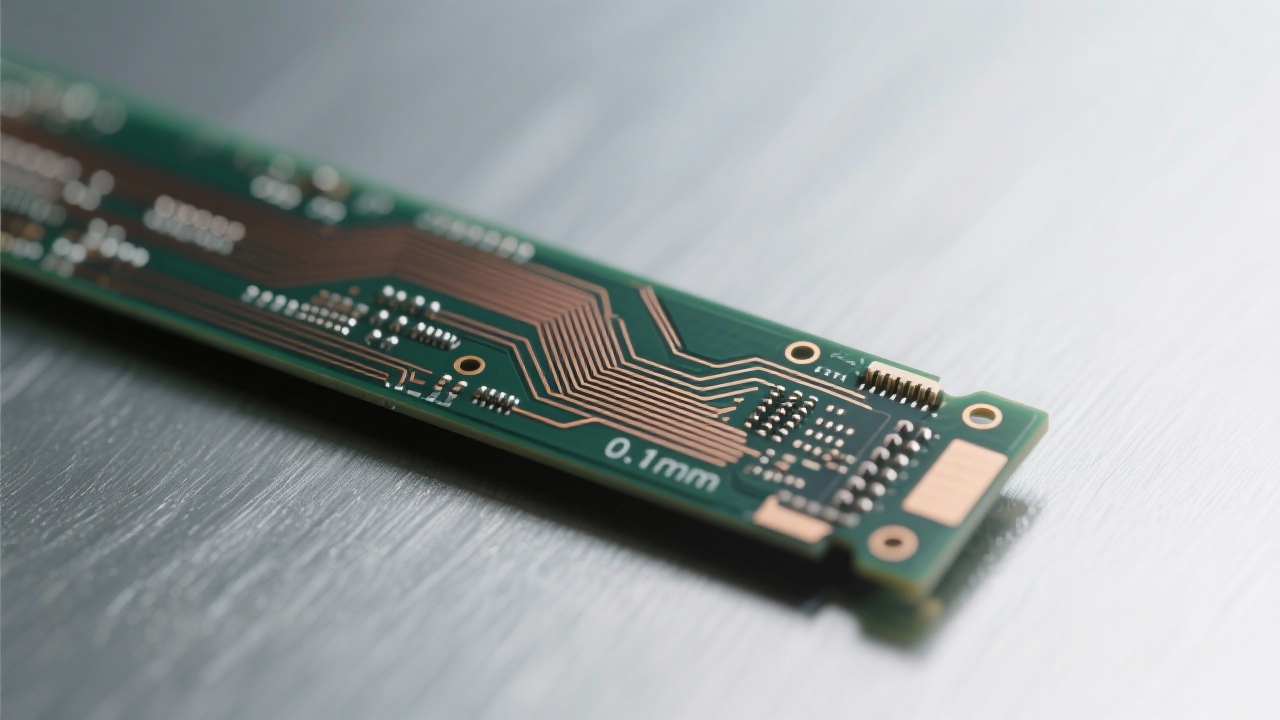

高频高速PCB通常采用低介电常数(Dk约为3.0-3.5)且低损耗正切(Df低于0.005)的聚四氟乙烯基或专用高频复合材料,以减小信号损耗和跨层干扰。制造过程中的叠层厚度控制必须严格,标准公差维持在±1%以内,防止阻抗曲线偏离设计目标。此外,铜箔粗糙度和表面处理工艺也显著影响高速信号阻抗匹配。

实时阻抗检测通过时域反射仪(TDR)测试关键走线阻抗,实现精细验证。结合自动光学检测(AOI)技术,能够高效识别走线宽度偏差及铜层缺陷,极大提升产品一致性与可靠性。借助设计仿真与制造检测双重保障,研发团队能快速反馈调整,缩短研发周期20%以上。

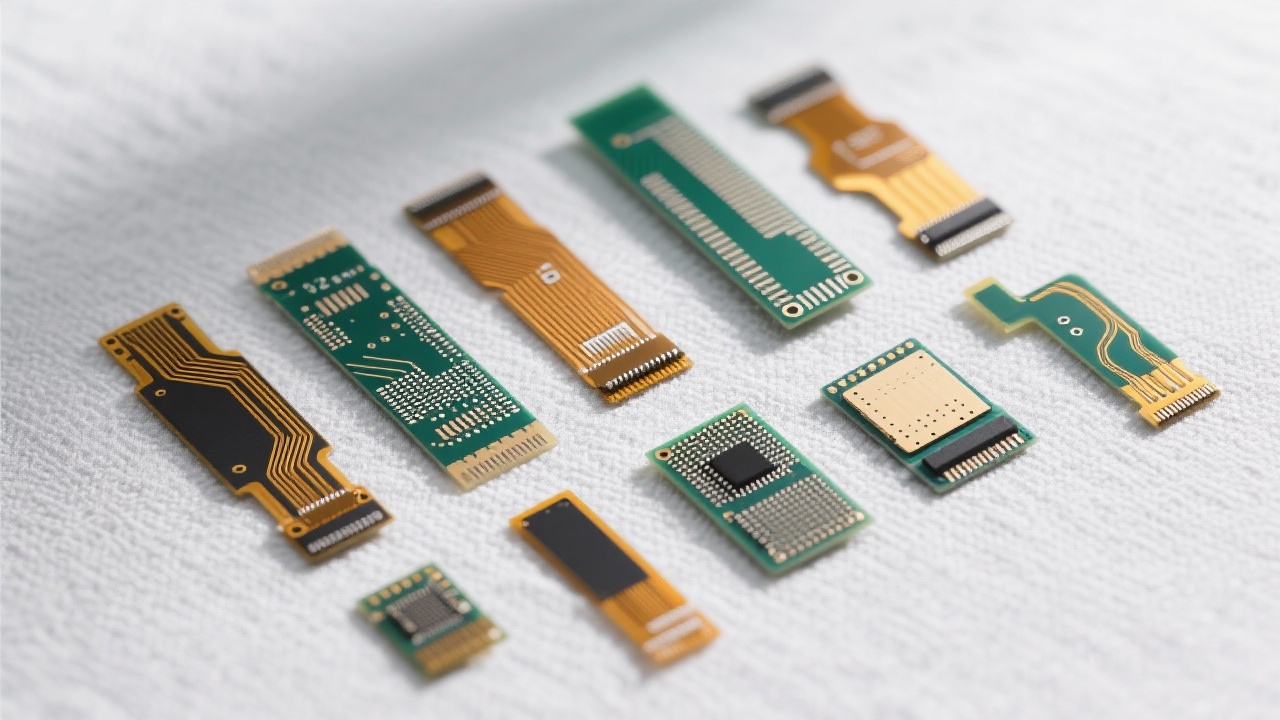

24层高频高速PCB产品集成了多层精密叠层技术,完美匹配50欧姆单端与100欧姆差分阻抗需求。采用进口高频介质材料,铜层均匀且厚度公差≤±3μm,保证稳定信号传输,适配5G基站、通信模块及高端高速计算平台。产品支持严苛的环境测试,抗温度及湿度变异能力强,满足电信行业对性能与耐用性的双重要求。

保障信号完整性与实现精密阻抗控制,是高速多层PCB制造的永恒追求。凭借先进材料选型、严格制造公差及科学测量验证,领先的高频高速PCB制造方案助力通信设备研发不断突破性能极限。