在5G和高频通信系统中,阻抗控制仍然是确保多层印刷电路板(PCB)信号完整性的关键。行业标准采用50Ω单端阻抗和100Ω差分阻抗值,这是出于优化信号传输速度和最大限度减少反射的考虑。这些参考阻抗直接影响插入损耗和串扰等参数,而这些参数对于在不降低性能的前提下维持高数据速率至关重要。

50 Ω 单端阻抗在功率处理能力和低衰减之间实现了理想的平衡,常用于射频电路和信号线。同时,100 Ω 差分阻抗支持差分对信号传输,利用互补信号增强抗噪性并降低电磁干扰 (EMI)。这种精确控制的阻抗值在高速数字电路设计中至关重要,因为即使是微小的偏差也可能导致信号反射和时序误差。

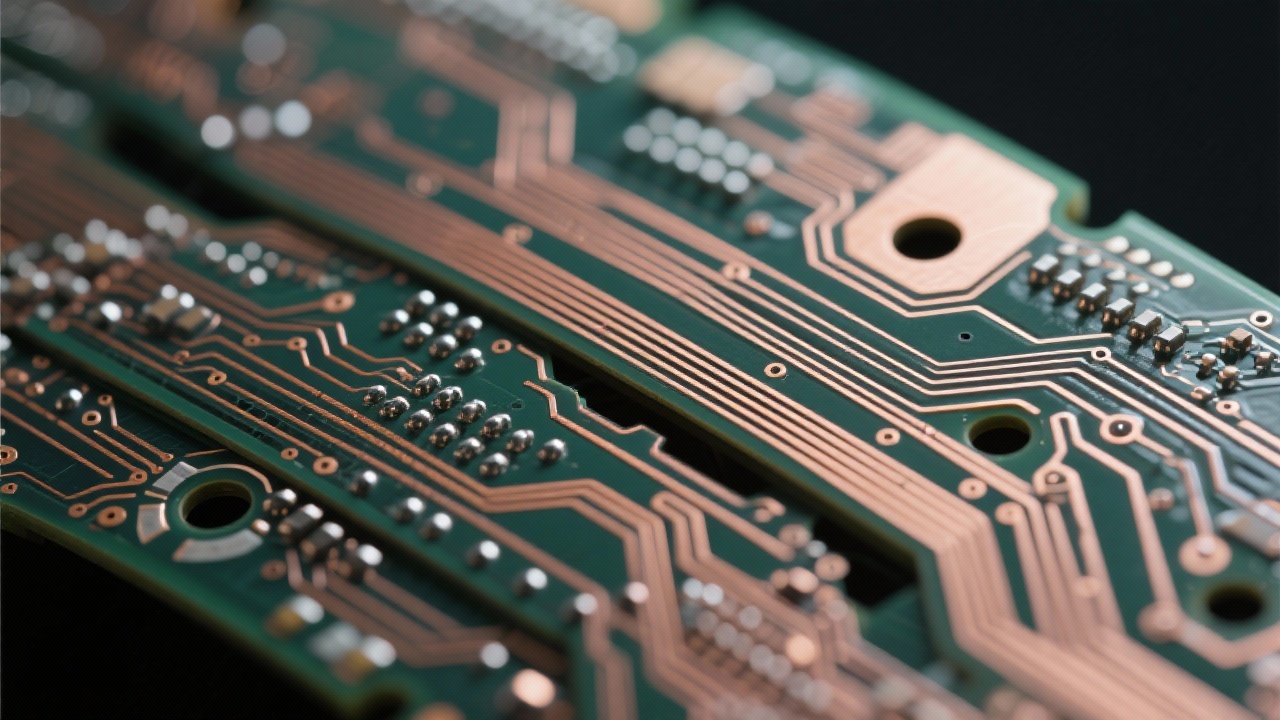

考虑在 5G 基站射频模块中应用阻抗控制。设计策略包括通过控制走线宽度、层叠结构和介质选择来形成精确的传输线,以满足 50 Ω 和 100 Ω 的目标阻抗。常见的缺陷,例如铜蚀刻公差不足或介质厚度不一致,通常会导致阻抗漂移,从而增加误码率 (BER)。

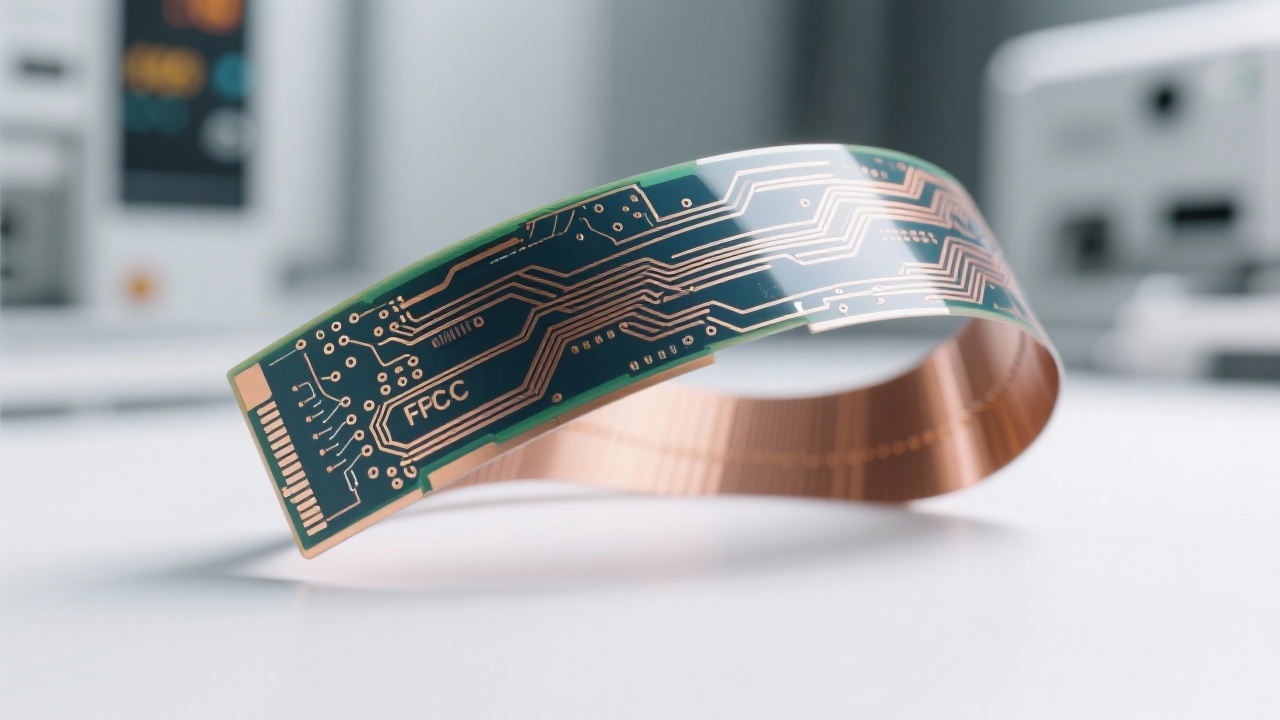

实际上,通常会采用窄至 3 mil(0.0762 毫米)的线宽,并结合焊锡掩膜定义的表面层,以抑制阻抗变化并保持规模化生产的重复性。其他技术包括填充焊锡掩膜下的过孔,以防止阻抗不连续和信号反射。

互动问题:您在高速PCB项目中是否遇到过阻抗漂移问题?哪些缓解策略取得了显著的改善?

材料的选择对阻抗稳定性至关重要。ISOLA 370HR和MENTRON6等高性能介电材料可提供稳定的介电常数(Dk ~3.7 至 4.0)和显著降低的损耗因子(Df < 0.005),从而最大限度地减少吉赫兹频率下的信号损耗。这些基板与厚度通常在 18 μm 至 35 μm 之间的铜箔配合使用,可实现对线路几何形状的精确控制。

此外,多层堆叠设计巧妙地分布接地层和电源层,从而实现可控阻抗通道布局,同时抑制电磁干扰。层压压力、树脂流量和固化周期均经过严格监控,以避免可能改变介质厚度并进而影响阻抗的偏差。

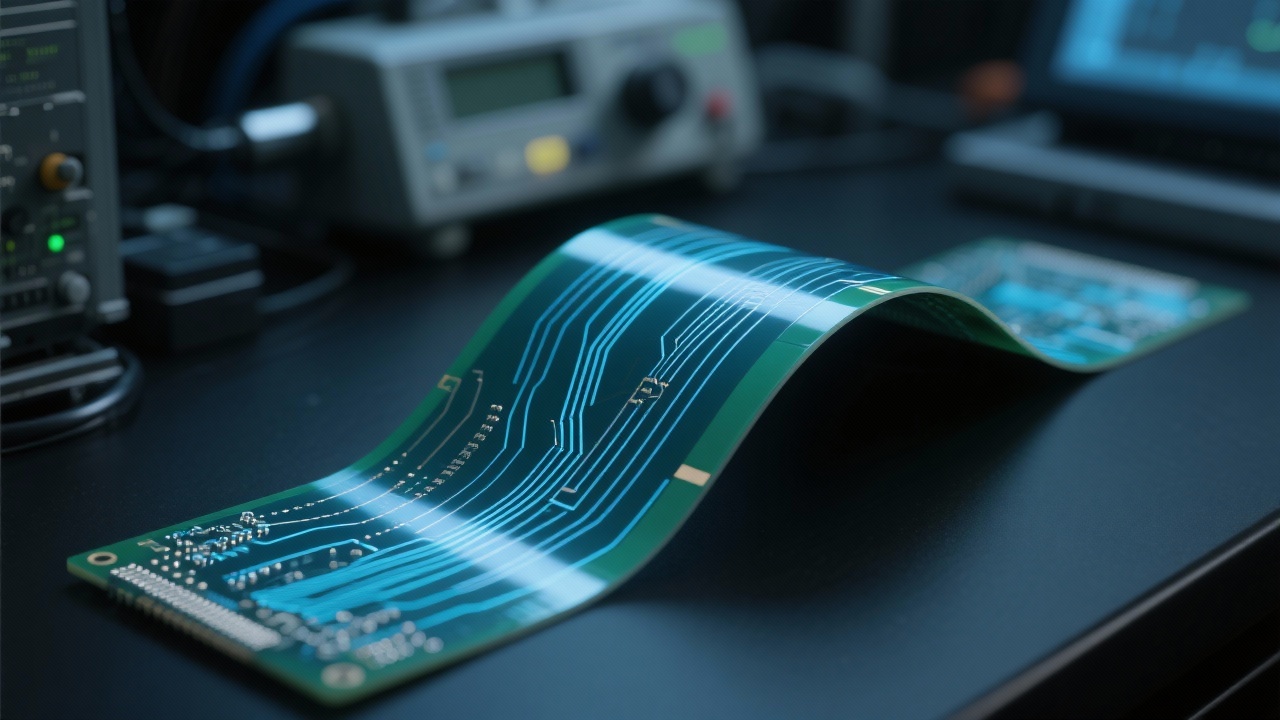

为了确保制造过程的完整性,工程师们利用先进的仿真工具——例如有限元法 (FEM) 和时域反射法 (TDR) 模型——在制造前预测阻抗特性。这些仿真整合了精确的材料参数和尺寸公差,从而将阻抗预测值控制在目标值的 ±5% 以内。

制造完成后,自动光学检测 (AOI) 系统会对铜线宽度、阻焊层覆盖率和过孔填充情况进行严格检测,以确保符合设计规范。这种严格的检测与稳定的良率和最低的返工成本密切相关。

-4.png?x-oss-process=image/resize,h_800,m_lfit/format,webp)