在高速信号传输中,阻抗匹配至关重要。当信号源、传输线和负载的阻抗不匹配时,会导致信号反射和失真。例如,在时钟频率为1GHz的高速PCB中,阻抗不匹配会导致高达30%的信号能量被反射回来,从而显著降低信号质量。业界已就50欧姆单端阻抗和100欧姆差分阻抗标准达成共识。这些标准广泛应用于各种高速通信系统,为工程师提供了统一的设计参考。

单端阻抗是指单根信号线与参考地之间的阻抗。在高速PCB设计中,常用的单端阻抗值为50欧姆。另一方面,差分阻抗是指差分对中两条互补信号线之间的阻抗。标准差分阻抗为100欧姆。

单端阻抗常用于通用信号传输,例如电源线和一些低速控制信号。差分阻抗主要用于高速数据传输接口,例如 USB 3.0、HDMI 和以太网。这些接口需要高速可靠的数据传输,而差分信号可以有效降低电磁干扰和串扰。

单端信号更容易受到外部干扰和接地噪声的影响。单端线路阻抗的任何变化都可能导致信号反射。差分信号由于其互补特性,可以抵消共模噪声。然而,如果差分信号对中两条线路的阻抗匹配不佳,也可能导致差模噪声,从而影响信号完整性。

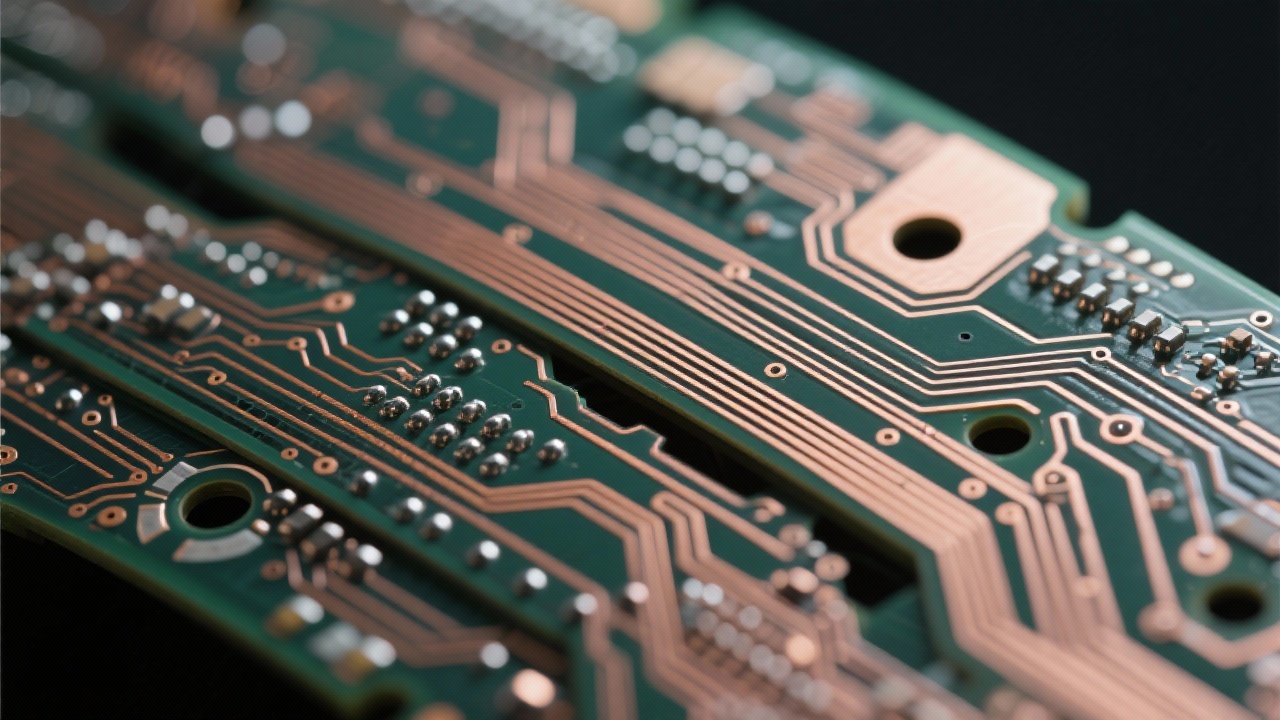

多种参数对阻抗稳定性有显著影响。介质的介电常数会影响信号在PCB中的传播速度。例如,介电常数高的介质会降低信号传播速度。铜箔厚度也很重要。较厚的铜箔可以降低信号线的电阻,但也会影响阻抗值。层叠结构是另一个关键因素。精心设计的层叠结构可以确保均匀的阻抗分布。例如,采用合理布局电源层、地层和信号层的四层PCB可以更好地控制阻抗。高速PCB设计中典型的线宽可能是3mil,使用阻焊层保护过孔也有助于保持阻抗稳定性。

以5G基站的PCB为例,在设计阶段,工程师需要预测并优化阻抗值。他们需要考虑5G信号的高频特性,例如24GHz至52GHz的高频范围。通过使用ISOLA 370HR和Panasonic MENTRON6等高性能介电材料,并精心设计层叠结构,工程师可以实现稳定的阻抗控制。在5G基站PCB设计中,精确的阻抗控制可以将信号损耗降低高达20%,从而提升基站的整体性能。

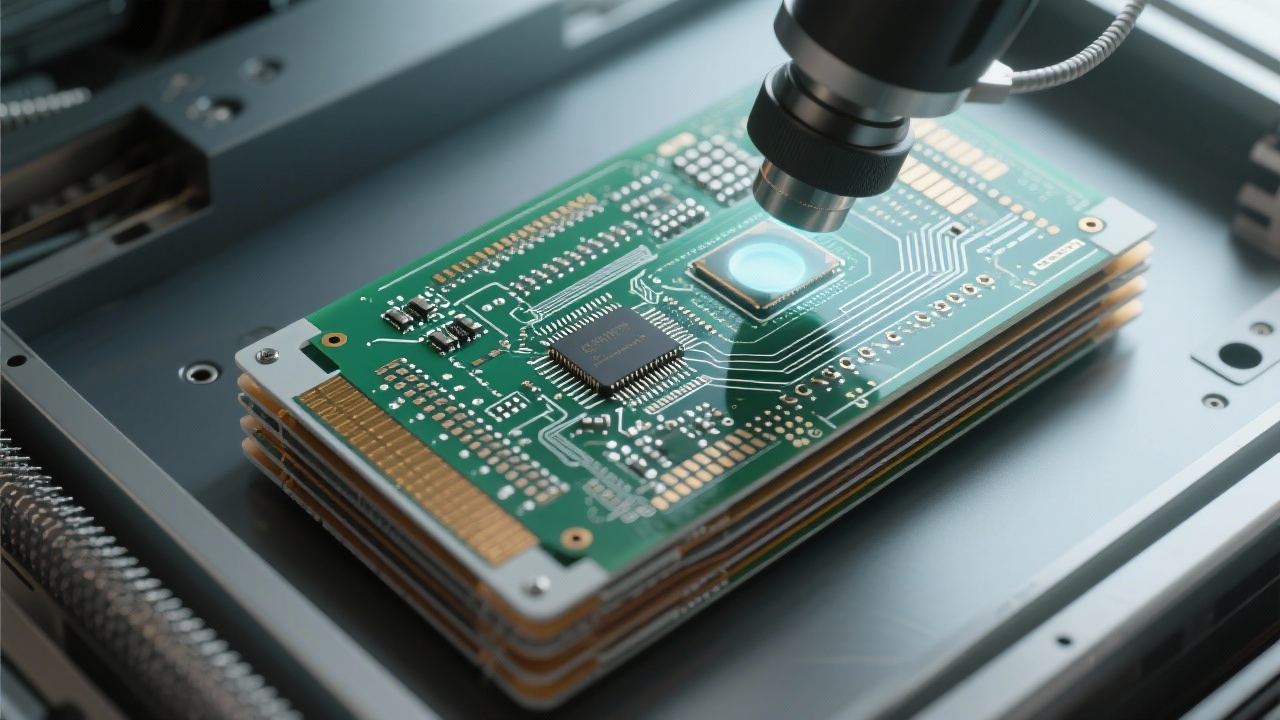

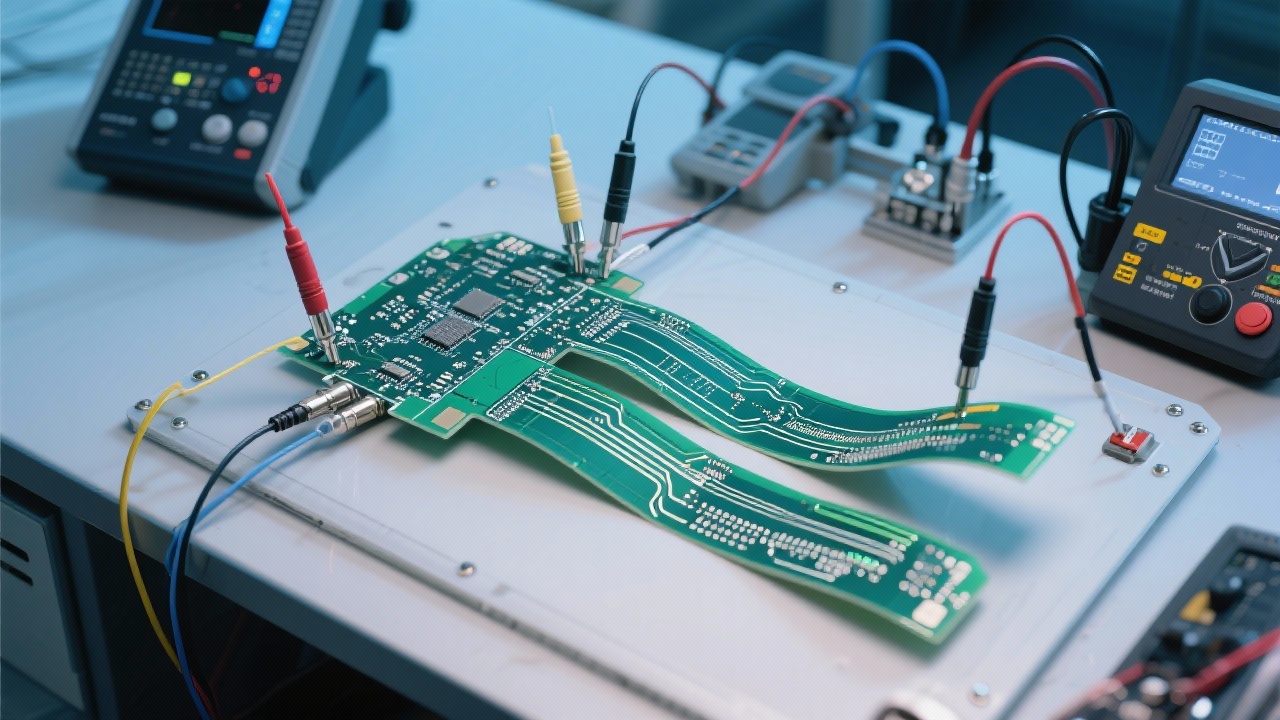

阻抗仿真工具,例如 HFSS 和 SIwave,在设计阶段被广泛应用。这些工具可以模拟 PCB 在不同工况下的阻抗特性,帮助工程师优化设计。AOI(自动光学检测)则应用于批量生产。它可以快速准确地检测 PCB 上的缺陷,例如短路和开路,这些缺陷可能会影响阻抗。通过结合这两种方法,工程师可以确保 PCB 在批量生产中的阻抗精度。

从设计、制造到测试,整个流程的质量控制至关重要。完善的质量控制体系能够提升客户信任度。通过严格把控每一个环节,从选用优质材料到采用先进的制造和测试技术,可以确保PCB的可靠性。这对于需要高性能、高稳定性PCB的新一代电信设备尤为重要。

欢迎咨询我们专为高频通信项目设计的高可靠性PCB解决方案。 点击此处了解更多信息。