随着对更快、更可靠的电信基础设施的需求激增,尤其是在5G基站和先进高频通信模块部署之后,确保印刷电路板(PCB)上的信号完整性变得至关重要。这一挑战的核心在于高速多层PCB的阻抗控制,即使是微小的偏差也会导致显著的信号劣化。本文探讨了高性能介电材料在稳定阻抗、降低信号反射和最大限度减少高频环境下的串扰方面所发挥的关键作用。

可控阻抗是高速PCB信号完整性的基石。业界通常采用两种阻抗标准:单端信号为50欧姆,差分对为100欧姆。这些标准确保在GHz频率下信号反射最小,时序裕量最佳。实际上,要达到这些阻抗值,需要精确控制介电常数(Dk)、导体几何形状和叠层结构。

印刷电路板上传输线的阻抗 (Z) 由以下关系决定:

Z = (87 / √(ε_r + 1.41)) * ln(5.98 * h / (0.8 * w + t))

其中ε_r为介电常数, h为介质层厚度, w为走线宽度, t为走线厚度。即使介电常数或物理尺寸的微小波动也会导致阻抗偏离规格范围。

5G网络运行在越来越高的频段(6GHz以下和毫米波频段),信号完整性方面的挑战也随之加剧。例如,射频前端模块中的差分对需要严格的阻抗匹配,以维持数据吞吐量并将误码率降低到10⁻¹²以下。

在一项涉及5G基站PCB的案例研究中,介电常数±5%的微小偏差会导致超过15%的阻抗失配,从而造成信号反射和信噪比(SNR)下降。这凸显了超稳定材料和精密制造工艺的重要性。

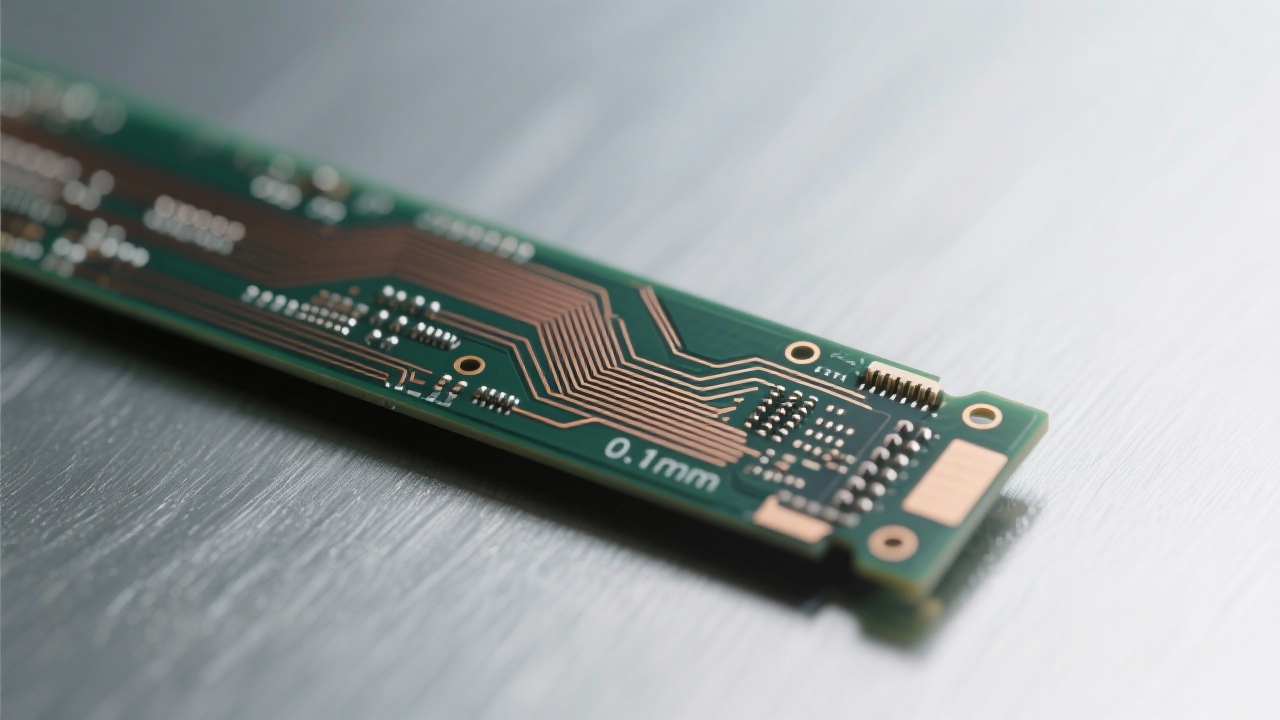

高性能介电基板,例如低损耗的罗杰斯材料、具有严格控制的介电常数 (Dk) 和损耗因子 (Df) 的先进 FR-4 变体,对于实现阻抗稳定性至关重要。这些材料的介电常数低至 3.3,Df 值低于 0.0017,远低于标准 FR-4。

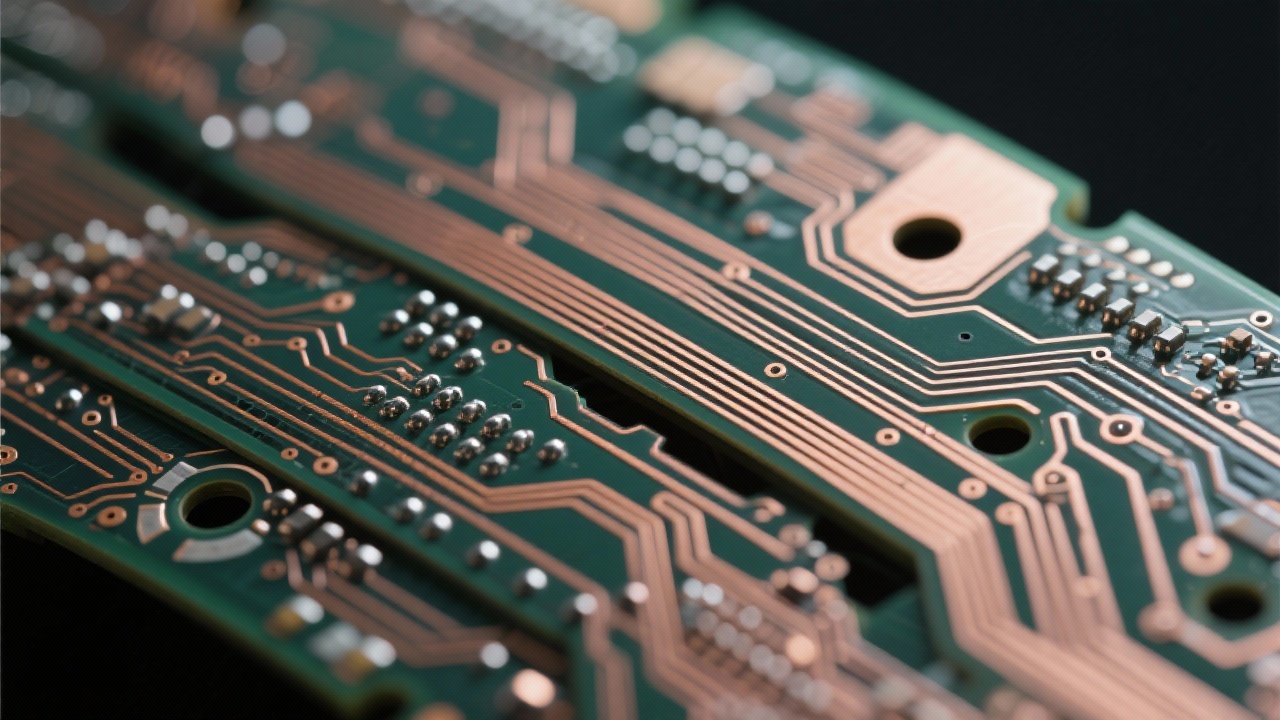

此外,精密层压工艺可实现高达±2微米的介电层厚度公差,从而减轻制造过程中引起的阻抗变化。采用对称叠层结构和可控走线几何形状的多层PCB可降低串扰和电磁干扰(EMI),进一步保持信号保真度。

在高速PCB制造中,通过仿真和物理测量验证阻抗一致性至关重要。电磁场仿真器可在制造前预测阻抗和耦合效应,从而提供精确的设计验证。生产完成后,时域反射仪(TDR)测量可对关键信号走线上的阻抗值进行经验性确认。

自动光学检测 (AOI) 通过检测可能影响阻抗性能的微观缺陷、层错位和线宽变化,进一步提升了质量控制。将这些技术集成到制造流程中,可将废品率降低高达 30%,并确保良率的稳定性。

您准备好利用尖端材料和精密制造工艺来提升您的高频PCB设计了吗?

探索我们的高性能PCB制造解决方案-4.png?x-oss-process=image/resize,h_800,m_lfit/format,webp)