In high-end HDI PCB exports, “meets IPC” is no longer a competitive endpoint—it’s a minimum entry ticket. The quiet shift happening across semiconductor test, advanced EMS, and high-mix SMT lines is this: while IPC Class II warp limits have long been treated as a practical benchmark (often referenced around 0.75%), many global buyers now screen suppliers at ≤0.50% warpage for HDI builds that must survive tight placement tolerances, probe contact stress, and repeated thermal cycling.

This matters because warpage is not just a board flatness number. In real production, it shows up as nozzle mis-picks, solder joint opens, test false-fails, and premature wear on expensive test sockets and probe pins.

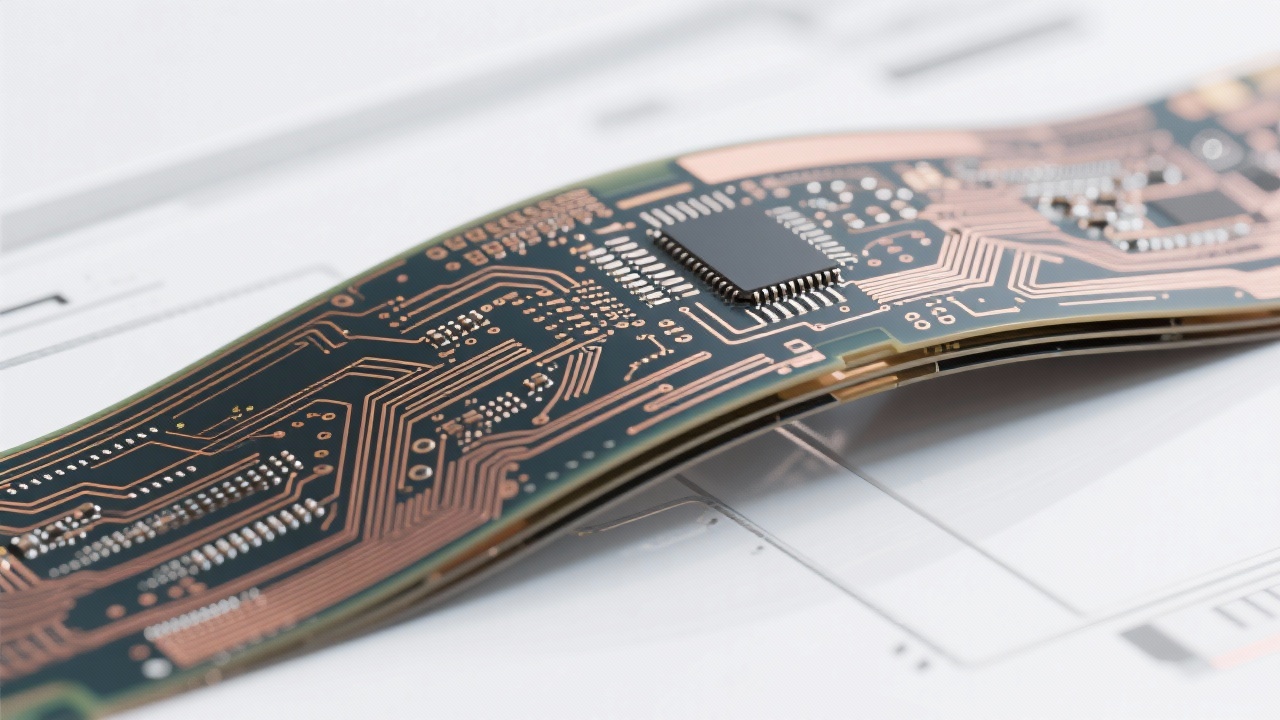

Warpage (or bow & twist) describes how far a PCB deviates from an ideal plane after fabrication, handling, or thermal exposure. It is typically expressed as a percentage: Warpage (%) = (Maximum deviation ÷ PCB length) × 100.

The number looks small—until it’s translated into millimeters. On a 200 mm panel or board, 0.75% implies up to 1.50 mm out-of-plane deviation, while 0.50% implies up to 1.00 mm. That 0.50 mm difference can decide whether a fine-pitch assembly line runs cleanly or spends the day firefighting.

For high-density interconnect boards used in semiconductor test equipment, high-layer-count controllers, or compact industrial modules, the tolerance stack is unforgiving: BGA coplanarity, stencil printing windows, pick-and-place Z-height profiles, and ICT/flying probe contact all assume a board that behaves predictably.

Historically, many supply chains referenced IPC Class II warpage limits as an acceptable baseline for general electronics. But in today’s export environment—especially for customers in North America, Germany, Japan, and high-end EMS hubs—the screening question has shifted from “Are you compliant?” to “Are you stable at scale?”

Three technical forces are behind the tightening demand to ≤0.50% warpage:

In other words, 0.50% is less about being strict and more about being predictable—a manufacturing maturity signal that engineers and procurement teams can trust.

HDI warpage often starts in the design stage. When the layer build-up is not structurally balanced—dielectric thickness, copper distribution, and build-up sequencing—stress vectors accumulate. A well-controlled symmetric architecture (commonly discussed in patterns such as 1:N:1, including advanced variants like 1:32:1 in high-layer designs) helps keep the neutral axis stable and reduces the tendency to “curl” after lamination and reflow.

Warpage is strongly correlated with copper imbalance across layers. Even when overall copper “looks” similar, localized heavy copper zones—power planes, shielding islands, dense via fields—create uneven CTE behavior during heating/cooling. Mature HDI producers use copper thickness compensation and pattern balancing to keep plating growth, etch-back, and final copper weight aligned with the intended mechanical symmetry.

In controlled mass production, a practical target is to maintain cross-board copper distribution variance within ±8–12% (application-dependent), while preventing “edge-heavy” plating growth that tends to pull panels into a saddle shape after pressing.

Buyers often hear “advanced equipment” in supplier pitches; the meaningful part is consistency. Stable lamination pressure/temperature uniformity, drill registration stability, and plating current distribution reduce lot-to-lot stress variation. In practical HDI export control, it’s not unusual to see capable lines hold warpage Cpk ≥ 1.33 on key products when the full chain—pressing, plating, and post-bake/conditioning—is tuned as one system rather than isolated steps.

In volume production for high-density assemblies, the value of lower warpage is most visible downstream—at SMT and test. The following figures are realistic reference ranges observed across advanced EMS environments (actual results vary by board size, thickness, component mix, and fixture design), comparing boards controlled around 0.75% versus 0.50%.

Note: Ranges are typical industry references for advanced SMT/test environments and should be validated against your board size, thickness, fixture planarity, and thermal process window.

The largest “hidden” benefit is not a single metric—it’s the reduction of process noise. When warpage variability tightens, engineers spend less time chasing intermittent symptoms, and procurement gets fewer quality escalations that disrupt the supply plan.

Warpage specifications are tightening for the same reason HDI itself became mainstream: electronics keep compressing functionality into smaller volumes. That trend increases the penalty for small mechanical deviations. At the same time, manufacturing technology has improved—meaning buyers now expect what once felt “premium.”

In many export RFQs, the warpage line item has shifted from a general statement to a measurable acceptance criterion linked to:

As a result, 0.75% may still satisfy baseline IPC references for many general electronics, but 0.50% increasingly functions as a quality filter for high-end HDI boards where downstream cost of failure is simply too high.

If your project involves high-end HDI PCB exports, semiconductor test fixtures, or tight SMT windows, the fastest way to de-risk sourcing is to review how warpage is controlled across stackup design → lamination → plating balance → final conditioning—with data, not promises.

Suggested SEO keywords integrated: HDI PCB warpage, IPC Class II warpage, 0.5% warpage standard, PCB flatness control, semiconductor test equipment PCB, high density interconnect board, SMT defect reduction.