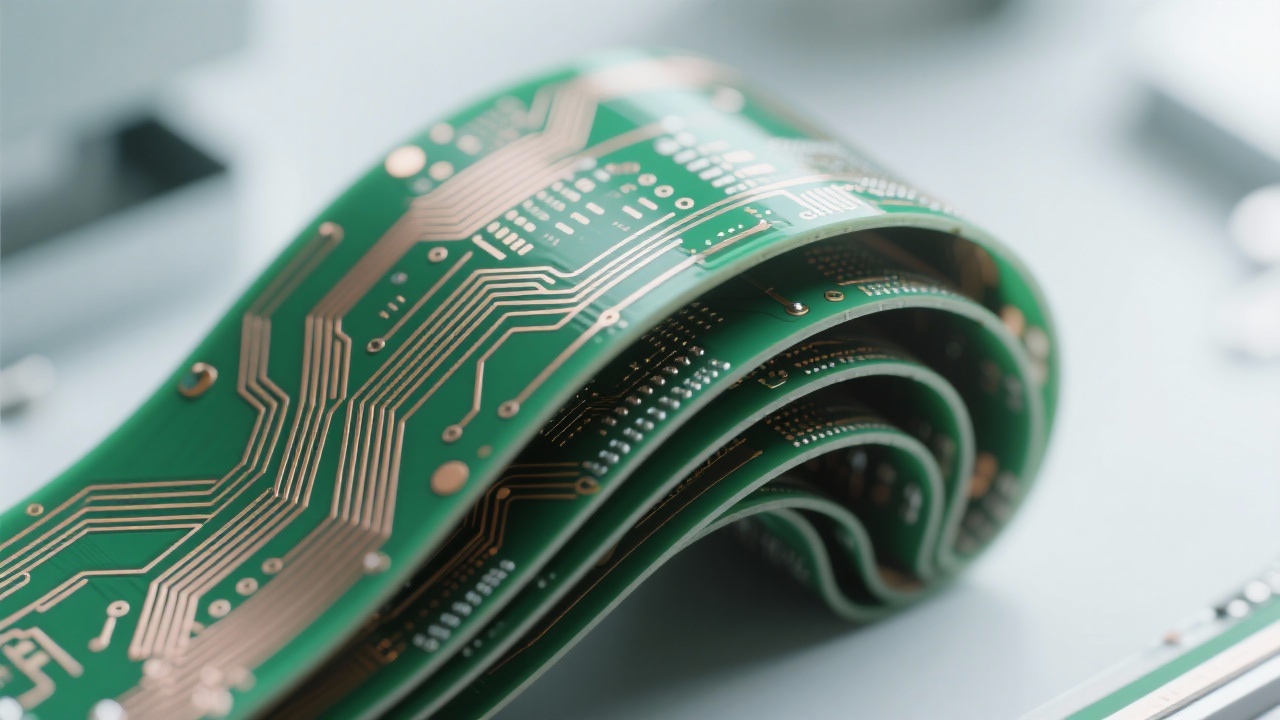

In the world of high-density interconnect (HDI) printed circuit boards, especially those used in semiconductor test equipment, one metric often overlooked by engineers and procurement teams alike is warpage — specifically, the 0.5% threshold defined in IPC-II standards. But this number isn’t arbitrary. It’s a performance benchmark that directly impacts yield, reliability, and long-term operational cost.

Warpage refers to the deviation from flatness in a PCB after manufacturing. For a 34-layer HDI board, even a small bend can cause misalignment during surface mount technology (SMT) assembly or poor contact between test probes and pads. According to real-world data from European EMS providers, boards with warpage exceeding 0.5% show up to 37% higher solder joint defect rates compared to those under 0.5%, especially when using fine-pitch components like BGA packages.

Achieving consistent warpage control requires more than just good material selection. It demands precision in:

A case study from a leading German PCB manufacturer shows that switching to such equipment reduced average warpage from 0.7% to 0.38%—resulting in a measurable drop in rework costs by 22% over six months.

EMS buyers who overlook warpage often pay the price later—not in upfront costs, but in hidden losses:

| Impact Area | Defect Rate Increase (vs. ≤0.5%) |

|---|---|

| SMT Assembly Yield | +37% |

| Probe Contact Reliability | -42% (more intermittent failures) |

| Test Equipment Downtime | +28% |

These aren't theoretical risks—they’re documented outcomes from production lines where warpage wasn't monitored closely enough.

Ready to future-proof your next HDI PCB project?

Get Your Free Warpage Control Checklist for HDI Boards