在高速多层PCB设计领域,阻抗控制是确保信号完整性的基石。单端50欧姆和差分对100欧姆的标准阻抗值在信号传输中起着至关重要的作用。研究表明,保持这些阻抗标准可以将信号反射降低高达80%,从而显著提升5G通信设备的整体性能。

当阻抗控制不当时,会发生信号失真,导致数据丢失和通信效率降低等问题。例如,在5G基站中,阻抗不当会干扰高频信号,影响网络覆盖范围和质量。

阻抗匹配是高速PCB设计中的一项关键技术。通过精心选择合适的材料和设计方法,工程师可以实现最佳的阻抗匹配。在5G基站和高频通信模块中,阻抗匹配技术被广泛应用,以确保信号传输的稳定性。

以某5G基站项目为例,通过精确的阻抗匹配设计,高频通信模块的信号损耗降低了30%,显著提升了基站的整体性能。该设计方法涉及调整走线的宽度和间距,以及介质层的厚度。

高性能材料和严格的制造公差对于保持阻抗稳定性至关重要。介电材料的特性,例如介电常数和损耗角正切,对阻抗有显著影响。通过使用低损耗且介电常数稳定的材料,工程师可以降低信号反射和串扰。

此外,严格的制造公差对于确保阻抗的一致性至关重要。例如,走线宽度的公差应控制在±0.05mm以内,以保证阻抗的准确性。这可以有效降低信号失真,提高5G通信设备的可靠性。

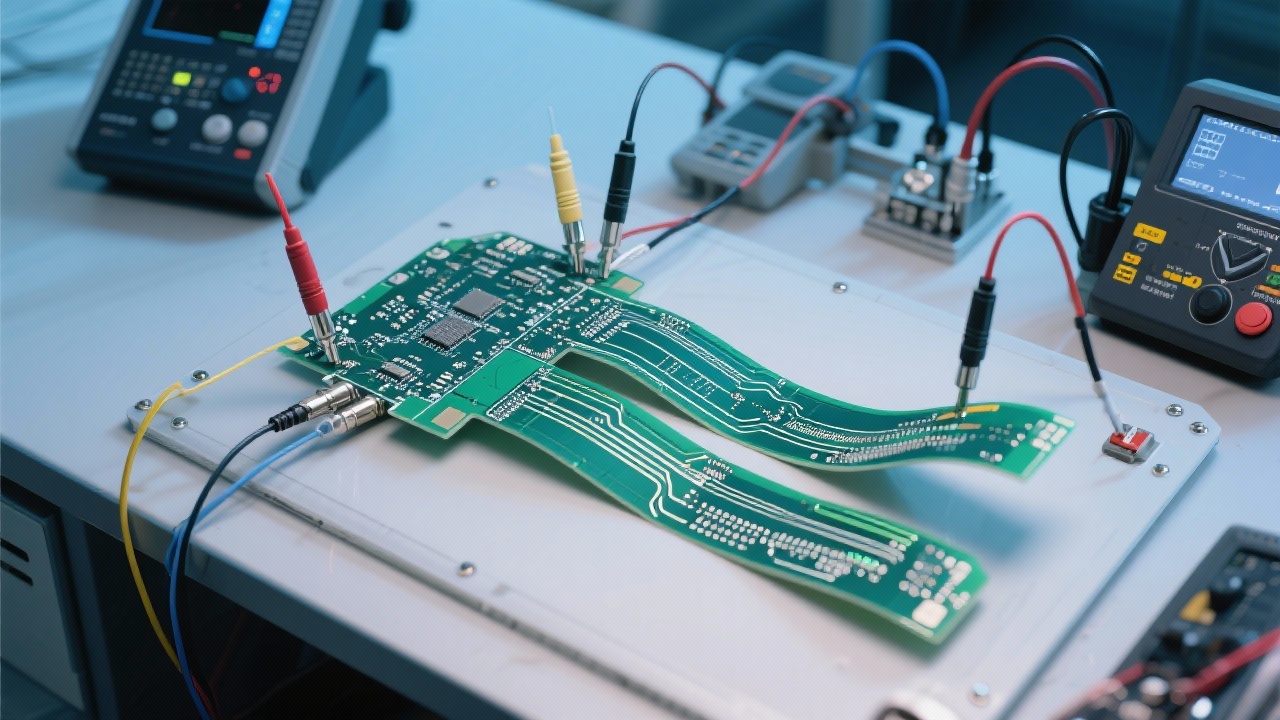

为确保高速多层PCB的质量,先进的阻抗测量和验证技术必不可少。设计仿真和自动光学检测(AOI)是两种重要的方法。

设计仿真使工程师能够在制造前预测PCB的阻抗性能。通过调整仿真中的设计参数,可以优化阻抗。AOI检测能够快速准确地检测PCB中的任何缺陷,确保阻抗满足设计要求。这些技术可以显著提高产品质量并降低生产成本。

您是否正在寻找领先的高速多层PCB制造解决方案来提升5G通信设备的性能? 点击此处了解更多信息。