在当今快速发展的电信领域,高速多层印刷电路板 (PCB) 是实现可靠高效数据传输的基石。精确的阻抗控制在保持信号完整性和最大限度减少高频应用(例如 5G 基站和先进电信硬件)中的传输错误方面起着至关重要的作用。本文深入探讨了复杂 PCB 设计中阻抗管理的关键技术细节,重点关注单端 50 欧姆和差分 100 欧姆阻抗标准,并结合实际案例研究,提出了切实可行的策略。

PCB走线阻抗决定了信号传输过程中遇到的阻力,直接影响信号质量和时序。单端阻抗保持在50欧姆,差分阻抗保持在100欧姆,可确保与射频元件和传输线实现最佳匹配,从而减少反射和串扰。偏差超过±10%的容差范围会降低误码率(BER),并损害系统整体可靠性,尤其是在数据速率超过10 Gbps的情况下。

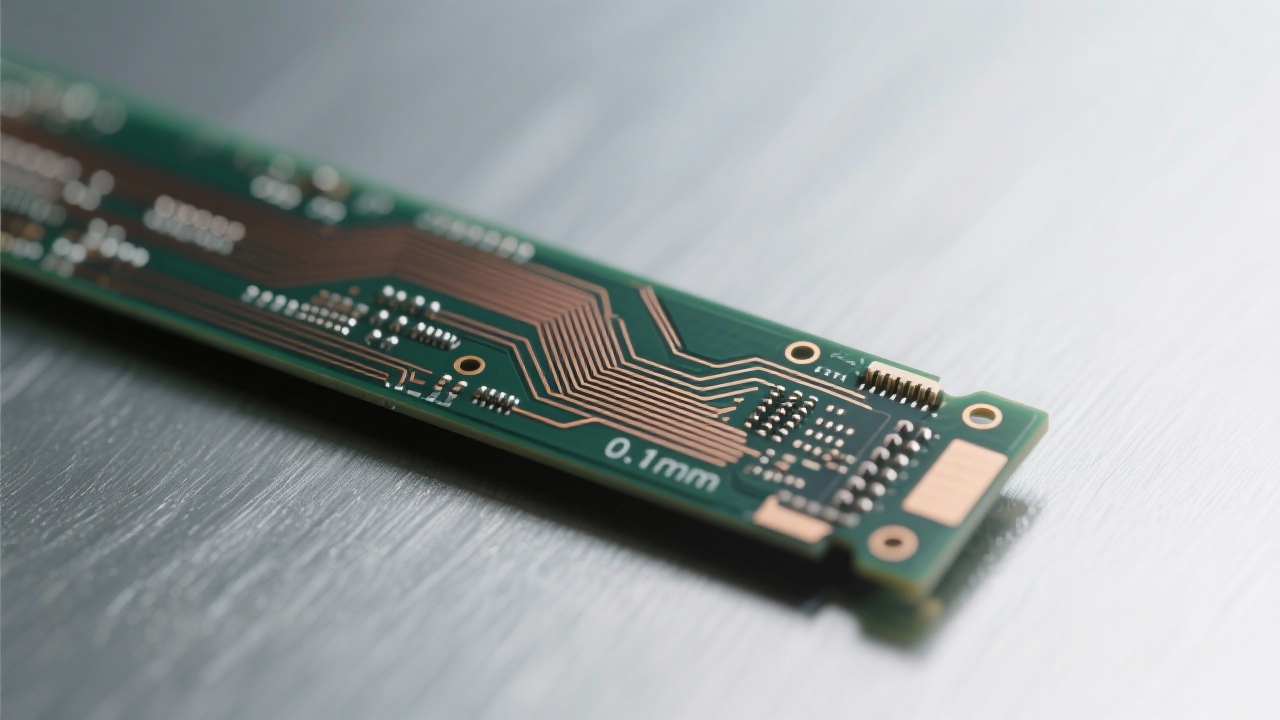

对于 5G 基站等电信应用而言,阻抗一致性至关重要。设计工程师采用精细的叠层结构和受控的走线几何形状,以满足严格的阻抗标准。例如,用于 PCIe Gen4 或 NR 接口层的差分对通常需要在整个传输路径上保持 100 ± 5 欧姆的差分阻抗,以保证眼图的完整性并降低信号失真。

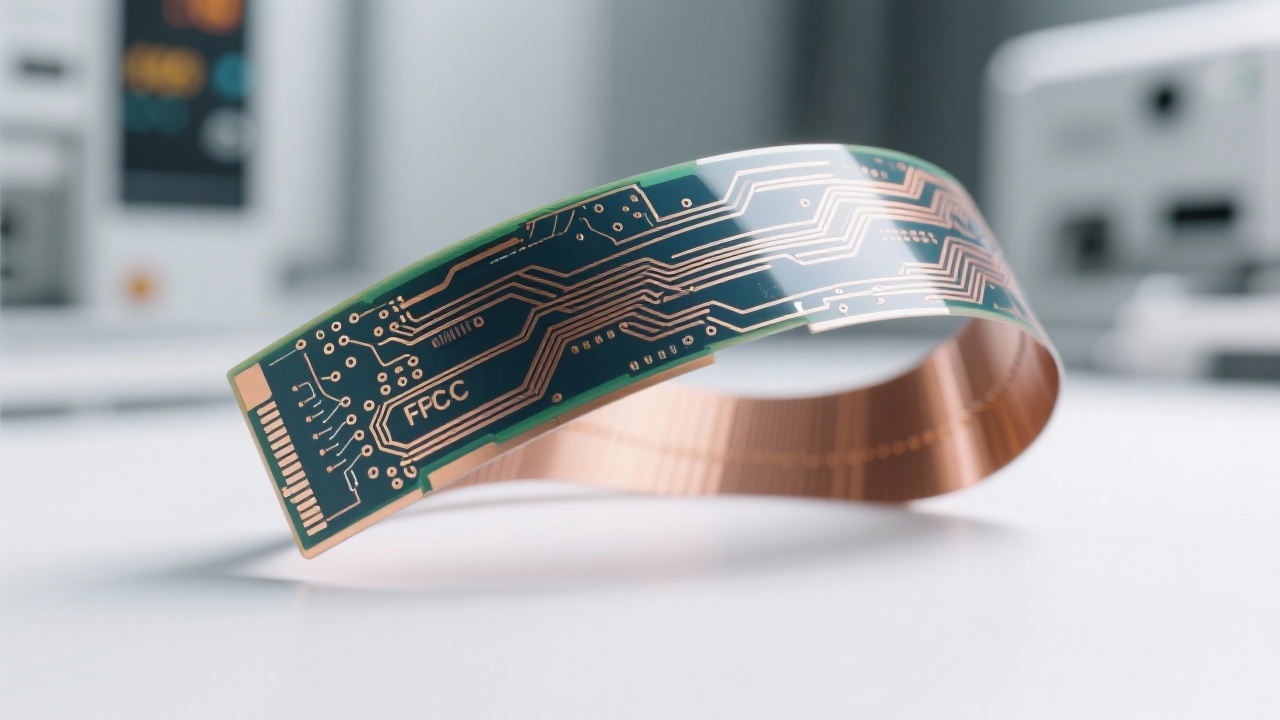

案例研究重点介绍了这些原则在多层PCB配置(涵盖12至24层)中的应用,这些配置集成了射频、电源和数字域,并采用了隔音技术。精确的阻抗匹配和强大的隔离相结合,有助于在密集的电信环境中实现持续的吞吐量,并减少电磁干扰(EMI)问题。

材料的选择对介电性能有着至关重要的影响,而介电性能又决定了固有的阻抗特性。诸如ISOLA 370HR和Panasonic MENTRON6等行业领先的材料具有卓越的热稳定性、低介电损耗(Dk ~3.7)和严格控制的厚度公差,这些特性直接提高了高频信号层的阻抗可预测性。

此外,先进的层压和压制工艺降低了层间差异,使不同生产批次间的阻抗偏差保持在±5%以内。这种高精度确保了设计阻抗与实际电路板性能相匹配,有效抑制了信号反射和近端串扰(NEXT),这对于高速数据完整性至关重要。

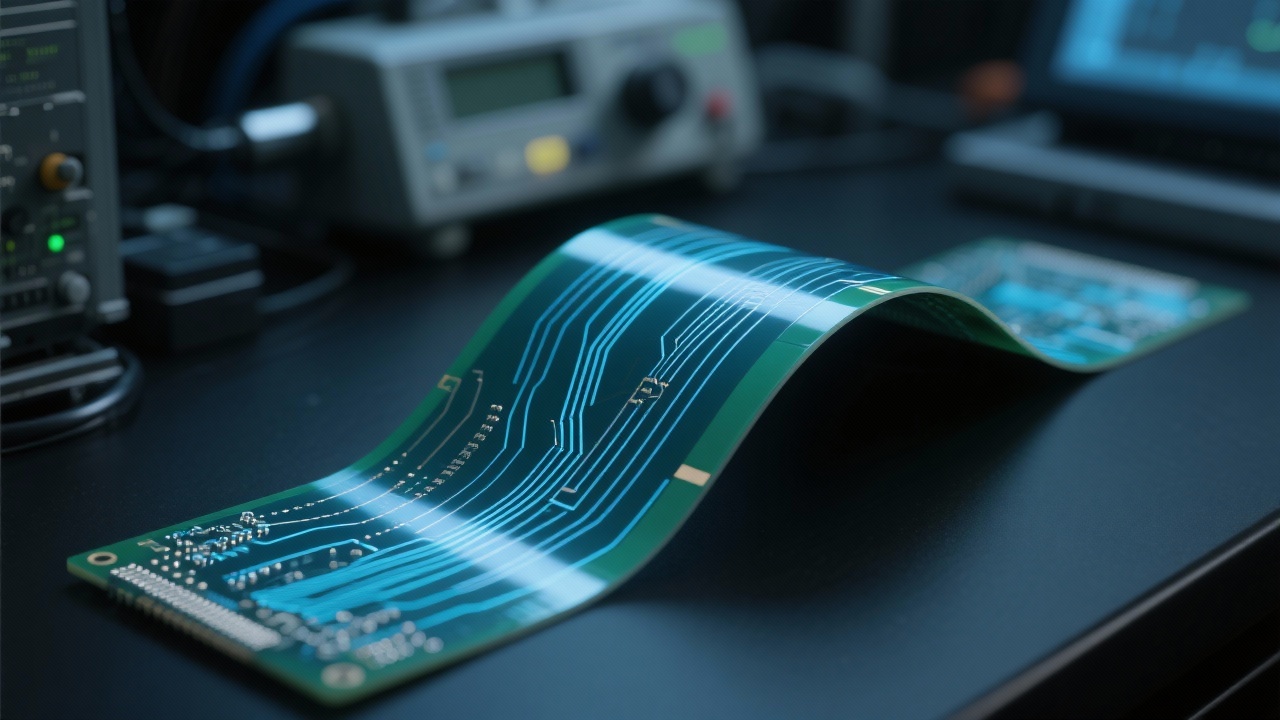

在制造之前,设计人员会使用诸如 Ansys HFSS 和 Keysight ADS 等电磁场仿真工具来验证阻抗分布并优化走线几何形状。这些仿真考虑了层间距、材料介电常数 (Dk) 和导体宽度等因素的变化,帮助工程师预测并减轻阻抗失配。

生产完成后,自动化光学检测 (AOI) 和时域反射仪 (TDR) 测试用于验证电路板的阻抗均匀性并识别缺陷。这些质量保证步骤对于确保多层 PCB 满足企业级质量要求,并在高数据速率和环境压力下可靠运行至关重要。

-1.png?x-oss-process=image/resize,h_800,m_lfit/format,webp)